## **DIGITAL ELECTRONICS**

#### Dr. Pradip Kumar Sahu Department of Information Technology

## Lecture of Module 1

Introduction to Digital Systems

## Overview

#### Introduction

- Digital and Analog Signals

- Logic Levels and Digital Waveforms

- Positive and Negative Logics

- Combinational and Sequential logics

- Types of Logic Devices

#### Introduction

Digital electronics is a field of electronics involving the study of digital signals and the engineering of devices that use or produce them.

This is in contrast to analog electronics and analog signals.

Digital electronic circuits are usually made from large assemblies of logic gates, often packaged in integrated circuits.

Complex devices may have simple electronic representations of Boolean logic functions.

# Analog versus Digital

- Most observables are analog

- But the most convenient way to represent and transmit information electronically is digital

- Analog/digital and digital/analog conversion is essential

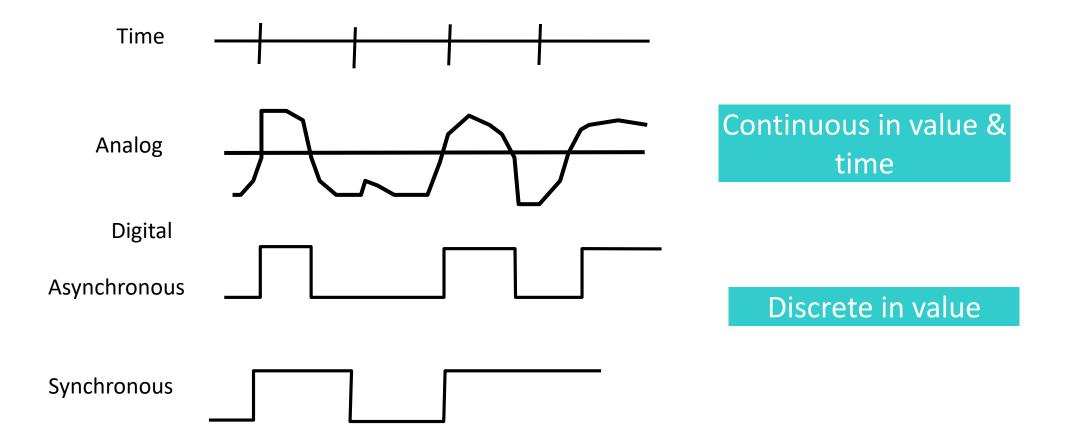

Analog Signals: The analog signals were used in many systems to produce signals to carry information. These signals are continuous in both values and time. In short, analog signals – all signals that are natural or come naturally are analog signals.

Digital Signals: Unlike analog signals, digital signals are not continuous but signals are discrete in value and time. These signals are represented by binary numbers and consist of different voltage values.

#### Difference Between Analog And Digital Signal

| Analog Signals                                                            | Digital Signals                                                  |

|---------------------------------------------------------------------------|------------------------------------------------------------------|

| Continuous signals                                                        | Discrete signals                                                 |

| Represented by sine waves                                                 | Represented by square waves                                      |

| Human voice, natural sound, analog<br>electronic devices are few examples | Computers, optical drives, and other electronic devices          |

| Continuous range of values                                                | Discontinuous values                                             |

| Records sound waves as they are                                           | Converts into a binary waveform.                                 |

| Only be used in analog devices.                                           | Suited for digital electronics like computers, mobiles and more. |

## Signal Examples Over Time

# Digital Signal

- ► An information variable represented by physical quantity.

- ► For digital systems, the variable takes on discrete values.

- Two level, or binary values are the most prevalent values in digital systems.

- Binary values are represented abstractly by:

- digits 0 and 1

- words (symbols) False (F) and True (T)

- ▶ words (symbols) Low (L) and High (H)

- and words On and Off.

- Binary values are represented by values or ranges of values of physical quantities

#### Binary Values: Other Physical Quantities

- ▶ What are other physical quantities represent 0 and 1?

- CPU: Voltage Levels

- Disk: Magnetic Field Direction

- CD: Surface Pits/Light

- Dynamic RAM: Electrical charge

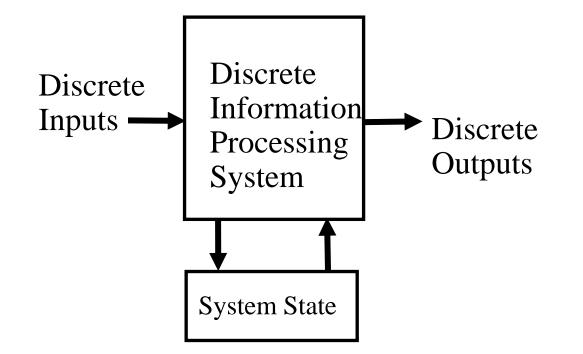

# **Digital System**

Takes a set of discrete information <u>inputs</u> and discrete internal information <u>(system state)</u> and generates a set of discrete information <u>outputs</u>.

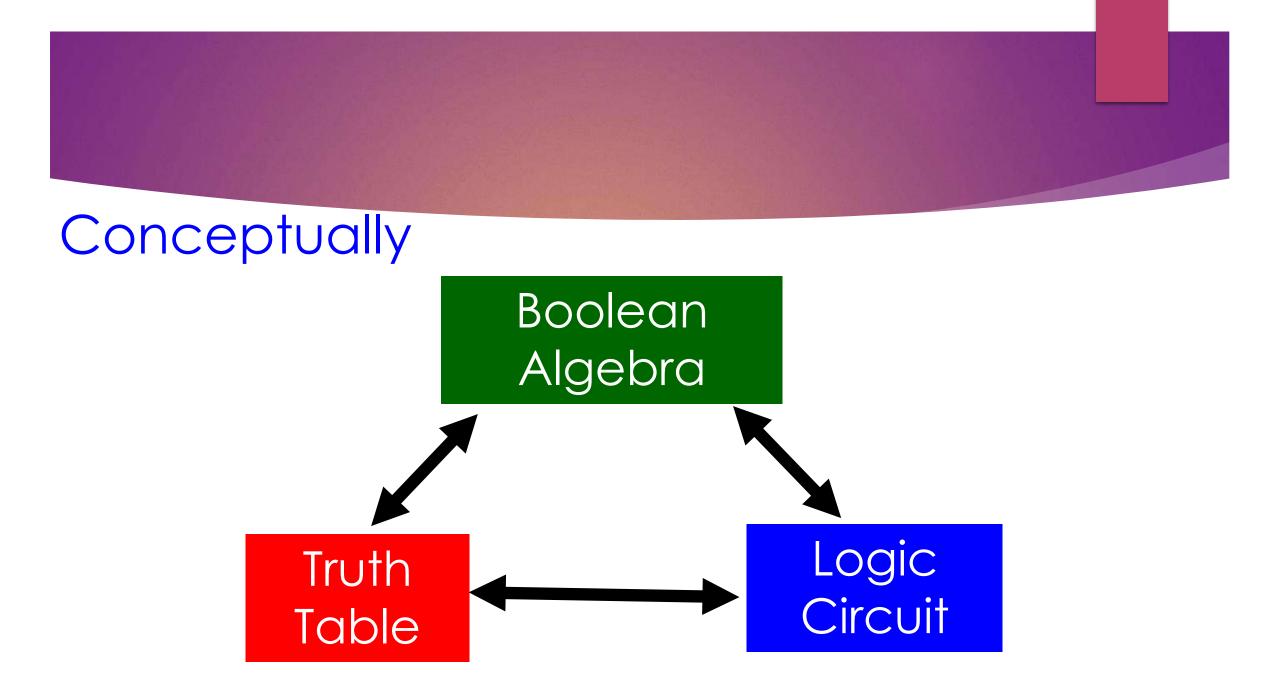

# Digital representations of logical functions

- Digital signals offer an effective way to execute logic. The formalism for performing logic with binary variables is called switching algebra or Boolean algebra.

- Digital electronics combines two important properties:

- ▶ The ability to represent real functions by coding the information in digital form.

- ► The ability to control a system by a process of manipulation and evaluation of digital variables using switching algebra.

- Digital signals can be transmitted, received, amplified, and retransmitted with no degradation.

- ▶ Binary numbers are a natural method of expressing logic variables.

- Complex logic functions are easily expressed as binary function.

- Digital information is easily and inexpensively stored

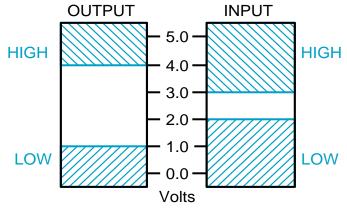

# Logic Levels

In digital circuits, a **logic level** is one of a finite number of states that a digital signal can inhabit. Logic levels are usually represented by the voltage difference between the signal and ground, although other standards exist. The range of voltage levels that represent each state depends on the logic family being used.

In binary logic the two levels are **logical high** and **logical low**, which generally correspond to binary numbers 1 and 0 respectively. Signals with one of these two levels can be used in Boolean algebra for digital circuit design or analysis.

| Logic level  | Active-high signal | Active-low signal |

|--------------|--------------------|-------------------|

| Logical high | 1                  | 0                 |

| Logical low  | 0                  | 1                 |

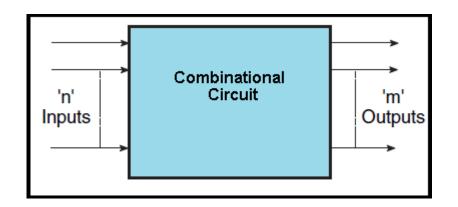

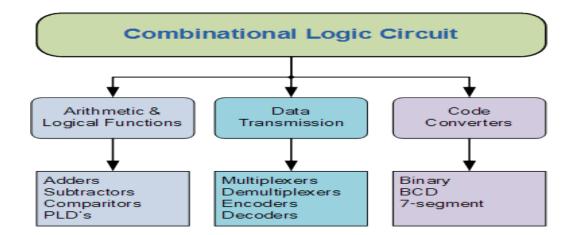

## Combinational Logic Circuit

The outputs of **Combinational Logic Circuits** are only determined by the logical function of their current input state, logic "0" or logic "1", at any given instant in time.

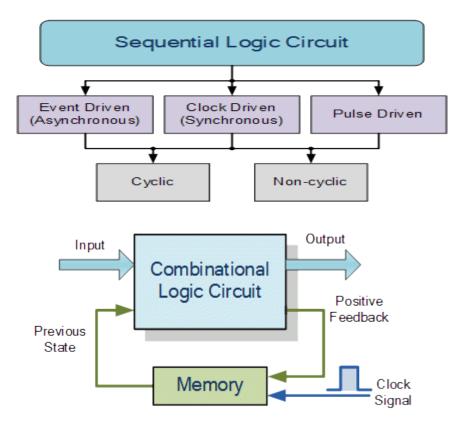

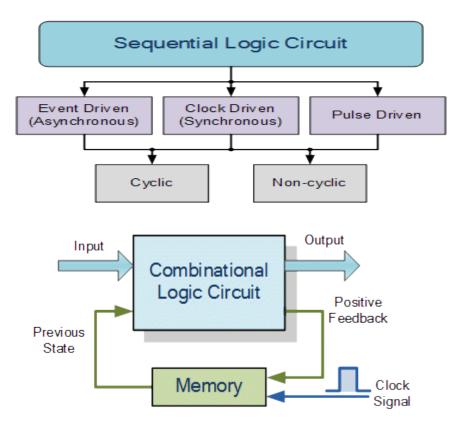

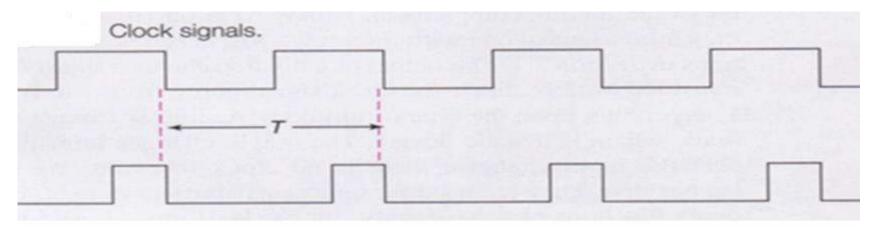

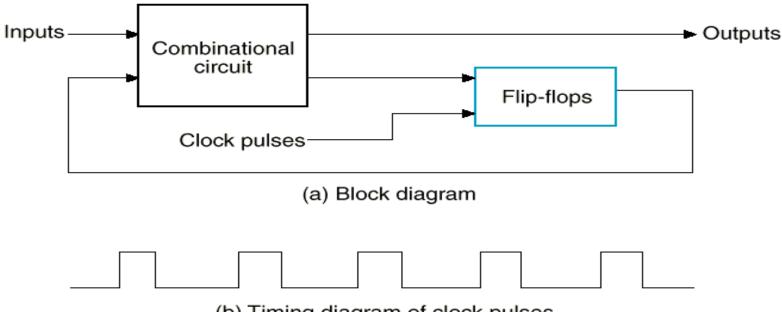

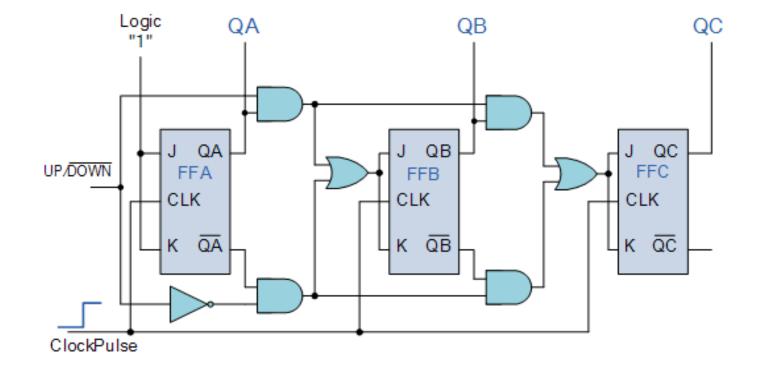

## Sequential Logic Circuits

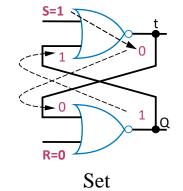

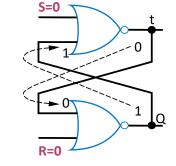

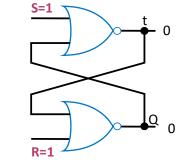

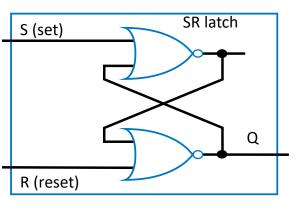

the output state of a "sequential logic circuit" is a function of the following three states, the "present input", the "past input" and/or the "past output". *Sequential Logic circuits* remember these conditions and stay fixed in their current state until the next clock signal changes one of the states, giving sequential logic circuits "Memory".

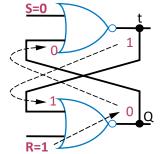

Sequential logic circuits are generally termed as *two state* or Bistable devices which can have their output or outputs set in one of two basic states, a logic level "1" or a logic level "0" and will remain "latched" (hence the name latch) indefinitely in this current state or condition until some other input trigger pulse or signal is applied which will cause the bistable to change its state once again.

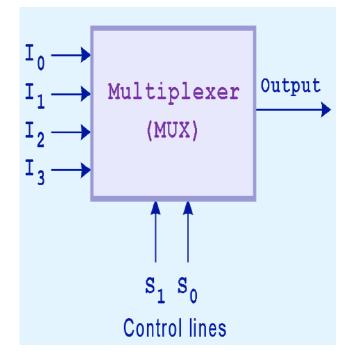

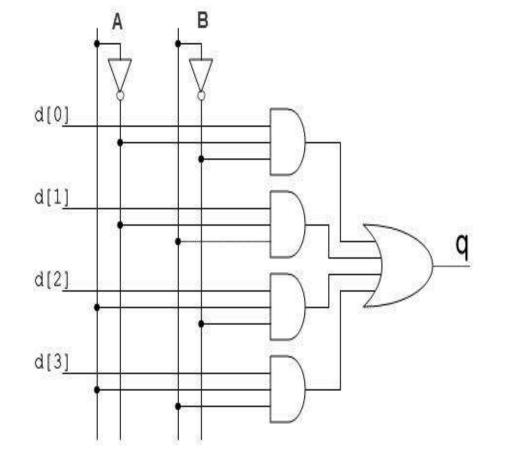

## Fixed function Logic devices

**Fixed logic device** such as a logic gate or a multiplexer or a flip-flop performs a given logic function that is known at the time of device manufacture

#### **Complexity Classification for Fixed-Function ICs**

SSI (Small-scale integration) – 10 gates– MSI (Medium-scale integration) – 10—100 gates LSI (Large-scale integration) – 100—10,000 gates VLSI (Very large-scale integration) – 10,000—100,000 gates ULSI (Ultra large-scale integration) -- >100,000 gates

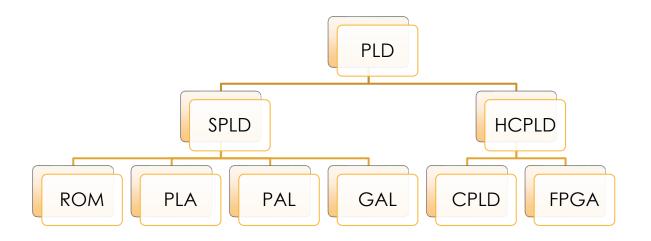

## Programmable Logic Devices

A programmable **logic device** can be configured by the user to perform a large variety of **logic functions** A **programmable logic device** (**PLD**) is an electronic component used to build reconfigurable digital circuits PLD has an undefined function at the time of manufacture

Before using PLD in a circuit it must be programmed (reconfigured) by using a specialized program

#### Purpose of PLD:

- Permits elaborate digital logic designs to be implemented by the user on a single device.

- ► Is capable of being erased and reprogrammed with a new design.

#### Advantages of PLDs

- Programmability

- ► Re-programmability

- > PLDs can be reprogrammed without being removed from the circuit board.

- Low cost of design

- Immediate hardware implementation

- less board space

- Iower power requirements (i.e., smaller power supplies)

- Faster assembly processes

- higher reliability (fewer ICs and circuit connections => easier troubleshooting)

- availability of design software

# Types of PLDs

- SPLDs (Simple Programmable Logic Devices)

- ROM (Read-Only Memory)

- PLA (Programmable Logic Array)

- PAL (Programmable Array Logic)

- ► GAL (Generic Array Logic)

- HCPLD (High Capacity Programmable Logic Device)

- CPLD (Complex Programmable Logic Device)

- ► FPGA (Field-Programmable Gate Array)

# PLD Configuration

- Combination of a logic device and memory

- Memory stores the pattern the PLD was programmed with

- ► EPROM

- ► Non-volatile and reprogrammable

- ► EEPROM

- ► Non-volatile and reprogrammable

- Static RAM (SRAM)

- ► Volatile memory

- ► Flash memory

- ► Non-volatile memory

- Antifuse

- ► Non-volatile and no re-programmability

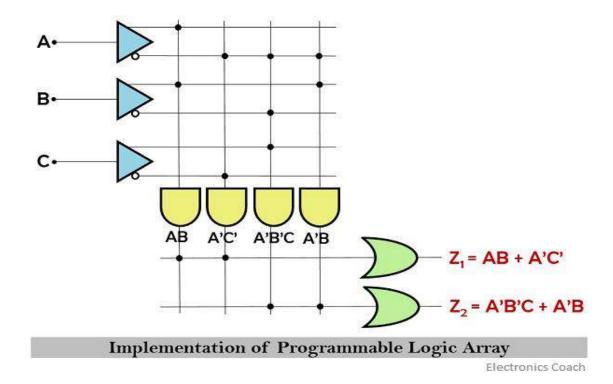

**PLA:** A programmable logic array (PLA) has a programmable AND gate array, which links to a programmable OR gate array

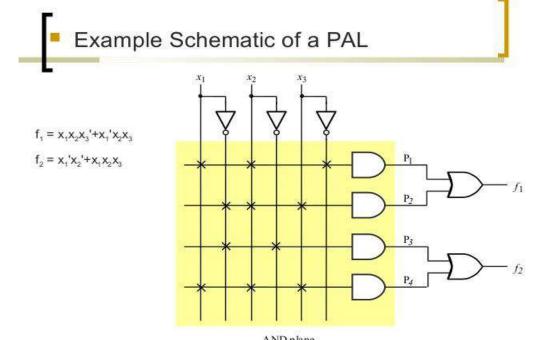

PAL: PAL devices have arrays of transistor cells arranged in a "fixed-OR, programmable-AND" plane

AND plane

GAL: An improvement on the PAL was the Generic Array Logic device

- This device has the same logical properties as the PAL but can be erased and reprogrammed

- The GAL is very useful in the prototyping stage of a design, when any bugs in the logic can be corrected by reprogramming

- GALs are programmed and reprogrammed using a PAL programmer

# HCPLD

CPLD (Complex Programmable Logic Device)

- ▶ Lies between PALs and FPGAs in degree of complexity.

- Inexpensive

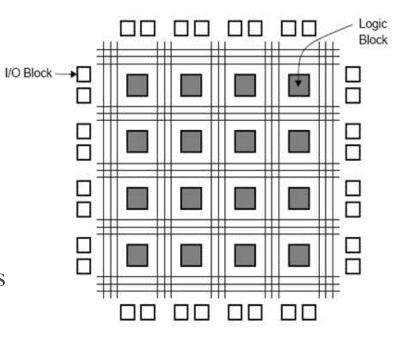

- ► FPGA (Field-Programmable Gate Array)

- ► Truly parallel design and operation

- Fast turnaround design

- Array of logic cells surrounded by programmable I/O blocks

FPGA

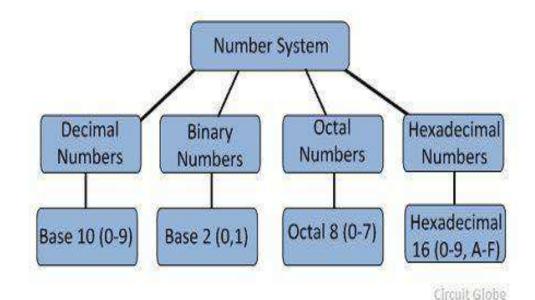

# Number Systems

#### Introduction

▶ Number Systems [binary, octal and hexadecimal]

#### **Number System conversions**

### Introduction

#### **Number System**

Code using symbols that refer to a number of items

#### **Decimal Number System**

Uses ten symbols (base 10 system)

#### **Binary System**

Uses two symbols (base 2 system)

#### **Octal Number System**

Uses eight symbols (base 8 system)

#### **Hexadecimal Number System**

Uses sixteen symbols (base 16 system)

- Numeric value of symbols in different positions.

- *Example* Place value in binary system:

| Place Value | 8s  | <b>4</b> s | 2s | 1s |

|-------------|-----|------------|----|----|

| Binary      | Yes | Yes        | No | No |

| Number      | 1   | 1          | 0  | 0  |

**RESULT**: Binary 1100 = decimal 8 + 4 + 0 + 0 = decimal 12

## **BINARY TO DECIMAL CONVERSION**

**Convert Binary Number 110011 to a Decimal Number:**

Binary 1 1 0 0 1 1  $\downarrow \downarrow \downarrow \downarrow \downarrow \downarrow \downarrow \downarrow$ Decimal 32 + 16 + 0 + 0 + 2 + 1 = 51

# Convert the following binary numbers into decimal numbers:

- Binary 1001 =

- Binary 1111 =

- Binary 0010 =

# Convert the following binary numbers into decimal numbers:

- Binary 1001 = 9

- Binary 1111 = 15

- Binary 0010 = 2

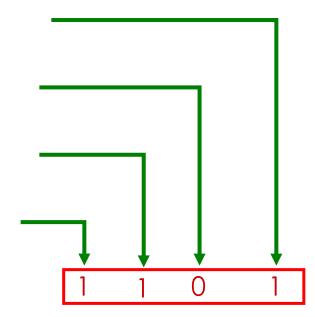

## **DECIMAL TO BINARY CONVERSION**

Divide by 2 Process

Decimal #

$$13 \div 2 = 6$$

remainder 1

$6 \div 2 = 3$  remainder 0

$3 \div 2 = 1$  remainder 1

$1 \div 2 = 0$  remainder 1

# Convert the following decimal numbers into binary:

- Decimal 11 =

- Decimal 4 =

- Decimal 17 =

# Convert the following decimal numbers into binary:

- Decimal 11 = 1011

- Decimal 4 = 0100

- Decimal 17 = 10001

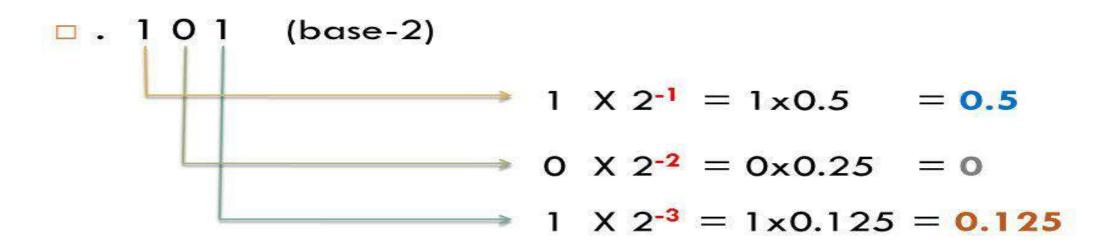

### **Binary-to-Decimal Conversion**

0.5 + 0 + 0.125 = 0.625

$0.101_2 = 0.625_{10}$

## **Converting Decimal Fraction to Binary**

- Convert N = 0.6875 to Radix 2

- Solution: Multiply N by 2 repeatedly & collect integer bits

| Multiplication     | New Fraction | Bit - | → First fraction bit            |

|--------------------|--------------|-------|---------------------------------|

| 0.6875 × 2 = 1.375 | 0.375        | 1     |                                 |

| 0.375 × 2 = 0.75   | 0.75         | 0     |                                 |

| 0.75 × 2 = 1.5     | 0.5          | 1 _   | $\rightarrow$ Last fraction bit |

| 0.5 × 2 = 1.0      | 0.0          | 1     |                                 |

- Stop when new fraction = 0.0, or when enough fraction bits are obtained

- Therefore,  $N = 0.6875 = (0.1011)_2$

- Check  $(0.1011)_2 = 2^{-1} + 2^{-3} + 2^{-4} = 0.6875$

## HEXADECIMAL NUMBER SYSTEM

| Uses 16 symbols | s -Base 16 Syste | em, 0-9, A, B, C, D, E, F |

|-----------------|------------------|---------------------------|

| Decimal         | <u>Binary</u>    | Hexadecimal               |

| 0               | 0000             | 0                         |

| 1               | 0001             | 1                         |

| 2               | 0010             | 2                         |

| 3               | 0011             | 3                         |

| 4               | 0100             | 4                         |

| 5               | 0101             | 5                         |

| 6               | 0110             | 6                         |

| 7               | 0111             | 7                         |

| 8               | 1000             | 8                         |

| 9               | 1001             | 9                         |

| 10              | 1010             | Α                         |

| 11              | 1011             | В                         |

| 12              | 1100             | С                         |

| 13              | 1101             | D                         |

| 14              | 1110             | E                         |

| 15              | 1111             | F                         |

| 16              | 0001 0000        | 10                        |

#### HEXADECIMAL AND BINARY CONVERSIONS

# Hexadecimal to Binary Conversion Hexadecimal Hexadecimal C Ginary 1100 0011

• Binary to Hexadecimal Conversion

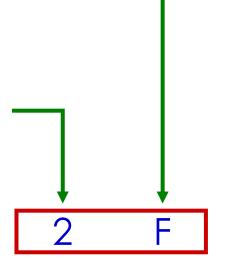

#### DECIMAL TO HEXADECIMAL CONVERSION

## Divide by 16 Process

Decimal # 47 ÷ 16 = 2 remainder 15

$2 \div 16 = 0$  remainder 2

CONVERSIONS WITH HEX

Decimal Fraction To Hex

- To convert Decimal fraction into Hex, multiply fractional part with 16 till you get fractional part o.

- Example : convert 0.03125<sub>10</sub> to Hex

Integer Part

| 0. 03125 * 16 =0.5 | 0 | Write |

|--------------------|---|-------|

| 0.03123 10 -0.3    | v | From  |

| 0.5 * 16 = 8.0     | 8 | Upto  |

|                    | • | Down  |

$\rightarrow 0.03125_{10} = 0.08_{16}$

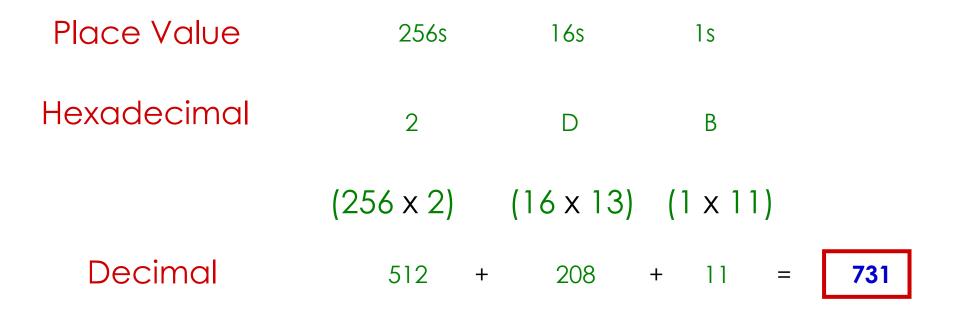

#### HEXADECIMAL TO DECIMAL CONVERSION

#### Convert hexadecimal number 2DB to a decimal number

# **Hexadecimal System**

The weight associated with each symbol in the given hexadecimal number can be determined by raising 16 to a power equivalent to the position of the digit in the number.

| Example | 4A90.2          | 2BC |                 |     |                      |      |      |                  |  |

|---------|-----------------|-----|-----------------|-----|----------------------|------|------|------------------|--|

| Digit   | 4               | А   | 9               | 0   | •                    | 2    | в    | С                |  |

| Weight  | 16 <sup>3</sup> | 16² | 16 <sup>1</sup> | 16º | Hexadecimal<br>Point | 16-1 | 16-2 | 16 <sup>-3</sup> |  |

| Example |                 |     |                 |     |                      |      |      |                  |  |

The following shows that the number (2AE)16 in hexadecimal is equivalent to 686 in decimal.

|     | 16 <sup>2</sup>   |   | 16 <sup>1</sup>    |   | 16 <sup>0</sup>        | Place values |

|-----|-------------------|---|--------------------|---|------------------------|--------------|

|     | 2                 |   | A                  |   | E                      | Number       |

| N = | $2 \times 16^{2}$ | + | $10 \times 16^{1}$ | + | $14 \times 16^{\circ}$ | Values       |

The equivalent decimal number is N = 512 + 160 + 14 = 686.

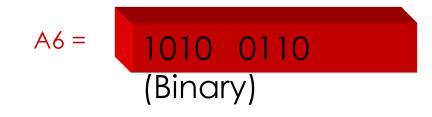

Convert Hexadecimal number A6 to Binary

Convert Hexadecimal number 16 to Decimal

Convert Decimal 63 to Hexadecimal

- Translate every hexadecimal digit into its 4-bit binary equivalent

- Examples:

- $(3A5)_{16} = (0011\ 1010\ 0101)_2$

- $(12.3D)_{16} = (0001\ 0010\ .\ 0011\ 1101)_2$

- $(1.8)_{16} = (0001 \cdot 1000)_2$

#### OCTAL NUMBERS

#### Uses 8 symbols -Base 8 System 0, 1, 2, 3, 4, 5, 6, 7

| Decimal | <b>Binary</b> | <u>Octal</u> |

|---------|---------------|--------------|

| 0       | 000           | 0            |

| 1       | 001           | 1            |

| 2       | 010           | 2            |

| 3       | 011           | 3            |

| 4       | 100           | 4            |

| 5       | 101           | 5            |

| 6       | 110           | 6            |

| 7       | 111           | 7            |

| 8       | 001 000       | 10           |

| 9       | 001 001       | 11           |

## • Binary to Octal Conversion

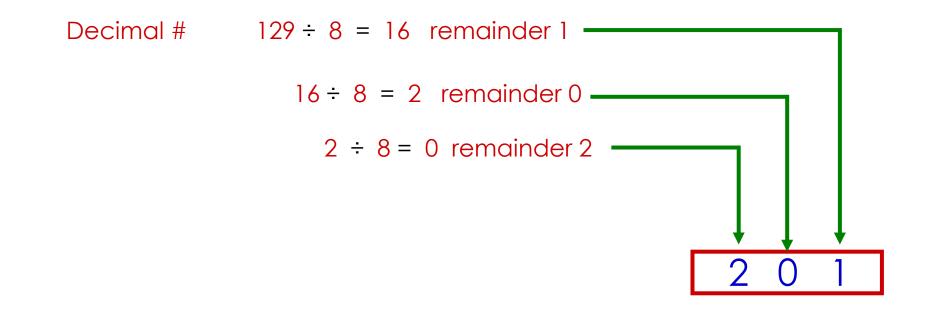

#### DECIMAL TO OCTAL CONVERSION

#### Divide by 8 Process

# Fraction Decimal to Octal Conversion - Example

Example: convert 0.356<sub>10</sub> to octal.

0.356 \* 8 = 2.848 → integer part = 2 0.848 \* 8 = 6.784 → integer part = 6 0.784 \* 8 = 6.272 → integer part = 6 0.272 \* 8 = 2.176 → integer part = 2 0.176 \* 8 = 1.408 → integer part = 1 0.408 \* 8 = 3.264 → integer part = 3, etc.

Answer =  $0.266213..._8$

The Hashemite University

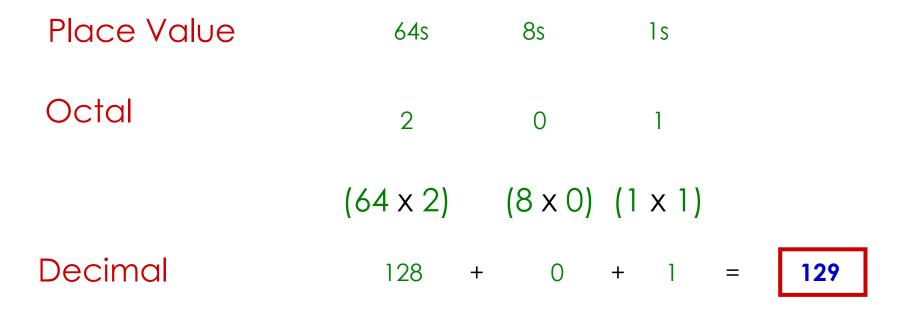

#### OCTAL TO DECIMAL CONVERSION

#### Convert octal number 201 to a decimal number

- Octal fraction to decimal

- Example

- Convert (23.25)8 to decimal

- 8<sup>1</sup> 8<sup>0</sup> . 8<sup>-1</sup> 8<sup>-2</sup>

- 2 3 2 5

- $= (2 \times 8^{1}) + (3 \times 8^{0}) + (2 \times 8^{-1}) + (5 \times 8^{-2})$

- = 16+3+0.25+0.07812

- = (19.32812)10

## Binary, Octal, and Hexadecimal

✤ Binary, Octal, and Hexadecimal are related:

Radix  $16 = 2^4$  and Radix  $8 = 2^3$

- Hexadecimal digit = 4 bits and Octal digit = 3 bits

- Starting from least-significant bit, group each 4 bits into a hex digit or each 3 bits into an octal digit

- Example: Convert 32-bit number into octal and hex

|   | 3 |   | 4 | 5 |   |   | 3 |   | 1 | 0 | R | 1 | 5 |   |   | 5 |   |   | 2 |   |   | 3 |   |   | 6 |   |   | 2 |   |   | 4 |   | Octal                |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|----------------------|

| 1 | 1 | 1 | L | D | 1 | 0 | 1 | 1 | 0 | 0 | 0 | 1 | 0 | 1 | 1 | 0 | 1 | 0 | 1 | 0 | 0 | 1 | 1 | 1 | 1 | 0 | 0 | 1 | 0 | 1 | 0 | 0 | <b>32-bit binary</b> |

| 2 | ] | E |   |   |   | ] | B |   |   |   | 1 |   |   |   | 6 |   |   | ŀ | 1 |   |   |   | 7 |   |   | 9 | 9 |   |   | 4 | 4 |   | Hexadecimal          |

Convert  $0.10111_2$  to base 8: **0.101\_110 = 0.56\_8** Convert 0.1110101 to base 16: **0.1110\_1010 = 0.EA\_{16}**

#### **Arithmetic Operations**

- Arithmetic Operations

- **Decimal Arithmetic**

- **Binary Arithmetic**

- **Signed Binary Numbers**

## Arithmetic Operations

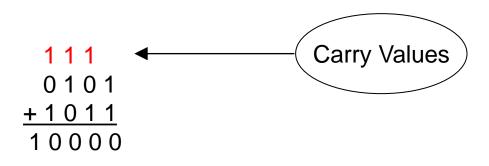

#### Addition

- Follow same rules as in decimal addition, with the difference that when sum is 2 indicates a carry (not a 10)

- ► Learn new carry rules

- ▶ 0+0 = sum 0 carry 0

- ▶ 0+1 = 1+0 = sum 1carry 0

- ▶ 1+1 = sum 0 carry1

- ▶ 1+1+1 = sum 1carry1

| Carry  | 1 | 1 | 1 | 1 | 1 | 0 |

|--------|---|---|---|---|---|---|

| Augend | 0 | 0 | 1 | 0 | 0 | 1 |

| Addend | 0 | 1 | 1 | 1 | 1 | 1 |

| Result | 1 | 0 | 1 | 0 | 0 | 0 |

## **Subtraction**

Learn new borrow rules

- ▶ 0-0 = 1-1 = 0 borrow 0

- ▶ 1-0 = 1 borrow 0

- ▶ 0-1 = 1 borrow 1

The rules of the decimal base applies to binary as well. To be able to calculate 0-1, we have to "borrow one" from the next left digit.

| Borrow     | 1 | 1 | 0 | 0 |   |

|------------|---|---|---|---|---|

| Minuend    | 1 | 1 | 0 | 1 | 1 |

| Subtrahend | 0 | 1 | 1 | 0 | 1 |

| Result     | 0 | 1 | 1 | 1 | 0 |

$\begin{array}{r}

1 & 2 \\

0 & 2 & 0 & 2 \\

1 & 0 & 1 & 0 \\

\underline{- & 0 & 1 & 1 & 1} \\

0 & 0 & 1 & 1

\end{array}$

# **Decimal Subtraction**

9's Complement Method

| 10's Complement Method                             | 72532          |

|----------------------------------------------------|----------------|

| 9's Complement Method                              | +96749         |

| Example: 72532 – 3250                              | <b>1</b> 69281 |

| 9's complement of 3250 is                          | +1             |

| 99999-03250=96749 If Carry, result is positive.    | 69282          |

| Add carry to the partial result                    |                |

| Example: 3250 – 72532                              | 03250          |

| 9's complement of 72532 is                         | + 2 7 4 6 7    |

| 99999-72532=27467 If no Carry, result is negative. | > 30717        |

| Magnitude is 9's complement of the result          | = -69282       |

|                                                    |                |

## **Decimal Subtraction**

- ▶ 9's Complement Method

- ▶ 10's Complement Method

10's Complement Method+96750Example: 72532 - 325016928210's complement of 3250 isIf Carry, result is positive.<br/>Discard the carryExample: 3250 - 725320325010's complement of 72532 is03250

$1\ 0\ 0\ 0\ 0\ -7\ 2\ 5\ 3\ 2\ =\ 2\ 7\ 4\ 6\ 8$ If no Carry, result is negative.

Magnitude is 10's complement of the result.

72532

30718

= -69282

# **Binary Subtraction**

- ▶ 1's Complement Method

- ► 2's Complement Method

1's Complement Method +0111011 $\mathbf{1}$  0001111 Example: 1010100 – 1000100 +11's complement of 1000100 is 0111011 0010000 If Carry, result is positive. Add carry to the partial result Example: 1000100 – 1010100 1000100 1's complement of 1010100 is 0101011 +0101011If no Carry, result is negative. 1101111 Magnitude is 1's complement of the result = -0010000

1010100

# **Binary Subtraction**

- 1's Complement Method

- 2's Complement Method

Example: 1010100 – 1000100

2's complement of 1000100 is 0111100 If Carry, result is positive.

Example: 1000100 – 1010100

2's complement of 1010100 is 0101100

If no Carry, result is negative.  $\rightarrow 1110000$ Magnitude is 2's complement of the result = -0010000

2's Complement Method

Discard the carry

0010000

1000100

+0101100

1010100

+0111100

1 0010000

# Signed Binary Numbers

▶ When a signed binary number is positive

- The MSB is '0' which is the sign bit and rest bits represents the magnitude

- ▶ When a signed binary number is negative

- The MSB is '1' which is the sign bit and rest of the bits may be represented by three different ways

- Signed magnitude representation

- Signed 1's complement representation

- Signed 2's complement representation

# Signed Binary Numbers

|                                                                         | <u>- 9</u>           | <u>+ 9</u>           |

|-------------------------------------------------------------------------|----------------------|----------------------|

| Signed magnitude representation                                         | 1 1001               | 0 1001               |

| Signed 1's complement representation                                    | 1 0110               | 0 1001               |

| Signed 2's complement representation                                    | 1 0111               | 0 1001               |

|                                                                         |                      |                      |

|                                                                         | <u>- 0</u>           | <u>+ 0</u>           |

| Signed magnitude representation                                         | <u>- 0</u><br>1 0000 | <u>+ 0</u><br>0 0000 |

| Signed magnitude representation<br>Signed 1's complement representation |                      |                      |

## Range of Binary Number

#### **Binary Number of n bits**

• General binary number:  $(2^n - 1)$

Signed magnitude binary number:  $-(2^{n-1}-1)$  to  $+(2^{n-1}-1)$

Signed 1's complement binary number:  $-(2^{n-1}-1)$  to  $+(2^{n-1}-1)$

Signed 2's complement binary number:  $-(2^{n-1})$  to  $+(2^{n-1}-1)$

# Signed Binary Number Arithmetic

- Add or Subtract two signed binary number including its sign bit either signed 1's complement method or signed 2's complement method

- The 1's complement and 2's complement rules of general binary number is applicable to this

- It is important to decide how many bits we will use to represent the number

- Example: Representing +5 and -5 on 8 bits:

- +5:00000101

- -5: 10000101

- So the very first step we have to decide on the number of bits to represent number

## **Digital Codes**

## Overview

- Introduction

- Binary Coded Decimal Code

- **EBCDIC Code**

- **Excess-3 Code**

- **Gray Code**

- ► ASCII Code

# Introduction

- Calculations or computations are not useful until their results can be displayed in a manner that is meaningful to people.

- We also need to store the results of calculations, and provide a means for data input.

- ► Thus, human-understandable characters must be converted to computerunderstandable bit patterns using some sort of character encoding scheme.

- ► As computers have evolved, character codes have evolved.

- Larger computer memories and storage devices permit richer character codes.

- ► The earliest computer coding systems used six bits.

- Binary-coded decimal (BCD) was one of these early codes. It was used by IBM mainframes in the 1950s and 1960s.

- In 1964, BCD was extended to an 8-bit code, Extended Binary-Coded Decimal Interchange Code (EBCDIC).

- ► EBCDIC was one of the first widely-used computer codes that supported upper *and* lowercase alphabetic characters, in addition to special characters, such as punctuation and control characters.

- ▶ EBCDIC and BCD are still in use by IBM mainframes today.

- Other computer manufacturers chose the 7-bit ASCII (American Standard Code for Information Interchange) as a replacement for 6-bit BCD codes.

- While BCD and EBCDIC were based upon punched card codes, ASCII was based upon telecommunications (Telex) codes.

- ▶ Until recently, ASCII was the dominant character code outside the IBM mainframe world.

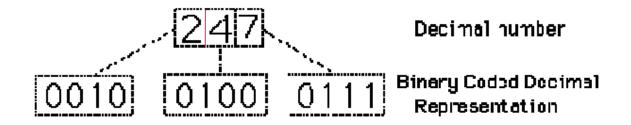

# Binary Coded Decimal (BCD)

| Convert | 0100 00 | 10 1000 00 | D10 BCDt | o decimal |

|---------|---------|------------|----------|-----------|

| 0100    | 0010    | 1000       | 0110     | BCD       |

| 4       | 2       | 8          | 6        | Decimal   |

| Decimal | <b>BCD code Representation</b> |

|---------|--------------------------------|

| 0       | 0000                           |

| 1       | 0001                           |

| 2       | 0010                           |

| 3       | 0011                           |

| 4       | 0100                           |

| 5       | 0101                           |

| 6       | 0110                           |

| 7       | 0111                           |

| 8       | 1000                           |

| 9       | 1001                           |

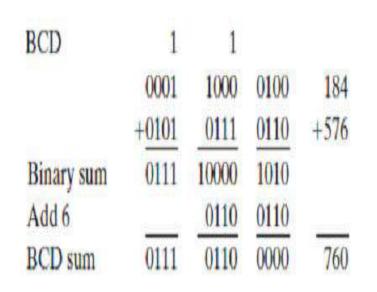

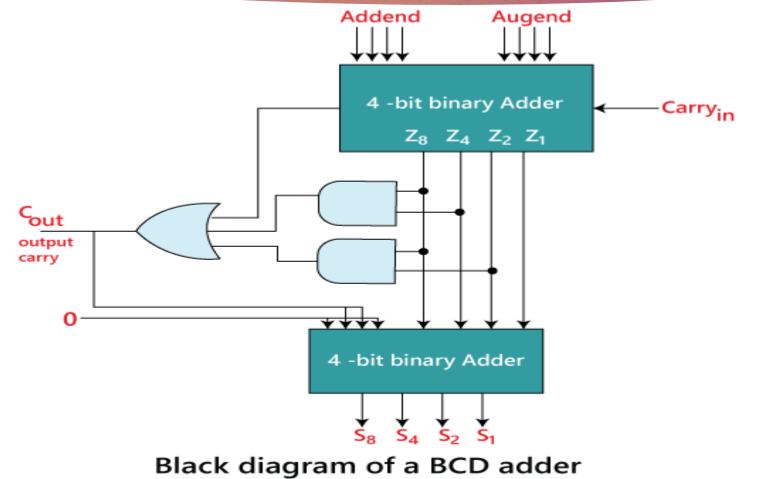

- Consider 5 + 5

- ► 5 0101

- $+5 \quad 0 \quad 1 \quad 0 \quad 1$

- giving 1010 which is binary 10 but not a BCD digit!

- ► What to do?

- Try adding 6??

- ▶ Had 1010 and want to add 6 or 0110

- ▶ so 1010

- ▶ plus 6 <u>0110</u>

- ► Giving 10000

- ► Add 7 + 6

- ▶ have 7 0 1 1 1

- ▶ plus 6 <u>0110</u>

- Giving 1101 and again out of range

- ► Adding 6 <u>0110</u>

- Giving 10011 so a 1 carries out to the next BCD digit

- FINAL BCD answer 0001 0011 or 13<sub>10</sub>

| 6         | 0110        | BCD for 6 | 42  | 0100 0010        | BCD for 42 |

|-----------|-------------|-----------|-----|------------------|------------|

| <u>+3</u> | <u>0011</u> | BCD for 3 | +27 | <u>0010 0111</u> | BCD for 27 |

| 9         | 1001        | BCD for 9 | 69  | 0110 1001        | BCD for 69 |

- Add the BCD for 417 to 195

- ▶ Would expect to get 612

- BCD setup start with Least Significant Digit

- $\blacktriangleright 0100 0001 0111$

- $\blacktriangleright 0001 1001 0101$

- ▶ 1100

- ► Adding 6 <u>0110</u>

- ► Gives 1 0010

- ▶ Had a carry to the 2<sup>nd</sup> BCD digit position

- ▶ 1

- 0100 0001 done

- $\blacktriangleright \quad \underline{0001} \quad \underline{1001} \quad 0010$

- ▶ 1011

- Again must add 6 0110

- ► Giving 1 0001

- And another carry

#### ► Had a carry to the 3rd BCD digit position

- ▶ 1

- $\blacktriangleright$  0100 done done

- $\blacktriangleright 0001 0001 0010$

- ► 0110

- And answer is 0110 0001 0010 or the BCD for the base 10 number 612

## **EBCDIC Code**

- ► The EBCDIC code is an 8-bit alphanumeric code that was developed by IBM to represent alphabets, decimal digits and special characters, including control characters.

- ► The EBCDIC codes are generally the decimal and the hexadecimal representation of different characters.

- ▶ This code is rarely used by non IBM-compatible computer systems.

## The Excess-3- Code

|   | DECIMAL      |          |       | BCD    |     | EXCESS-3      |               |               |          |

|---|--------------|----------|-------|--------|-----|---------------|---------------|---------------|----------|

|   | 0            |          |       | 0000   |     | 0011          |               |               |          |

|   | 1            |          |       | 0001   |     | 0100          |               |               |          |

|   | 2            |          |       | 0010   |     | 0101          |               |               |          |

|   | 3            |          |       | 00     | 11  | 0110          |               |               |          |

|   | 4            |          |       | 01     | 00  | 0111          |               |               |          |

|   | 5            |          |       | 0101   |     | 1000          |               |               |          |

|   | 6            |          |       | 0110   |     | 1001          |               |               |          |

|   | 7            |          |       | 0111   |     | 1010          |               |               |          |

|   | 8            |          |       | 1000   |     |               |               |               |          |

|   | 9            |          |       | 10     | 01  | 1100          |               |               |          |

|   | (a) 13       |          |       | (b) 43 | 60  |               |               |               |          |

|   | 1            | 3        |       |        | (b) | 4             | 3             | 0             |          |

| + | <u>3</u>     | <u>3</u> |       |        |     | $\frac{3}{7}$ | $\frac{3}{6}$ | $\frac{3}{3}$ |          |

|   | 4            | 6        |       |        |     | 7             | 6             | 3             |          |

|   | 0100 0110 Ex |          | Exces | ss-3   |     | 0111          | 0110          | 0011          | Excess-3 |

Excess-3 code is self complementary code? Justify.

## Gray Code

- Gray code is another important code that is also used to convert the decimal number into 8-bit binary sequence. However, this conversion is carried in a manner that the contiguous digits of the decimal number differ from each other by one bit only

- ► In pure binary coding or 8421 BCD then counting from 7 (0111) to 8 (1000) requires 4 bits to be changed simultaneously

- ► Gray coding avoids this since only one bit changes between subsequent numbers

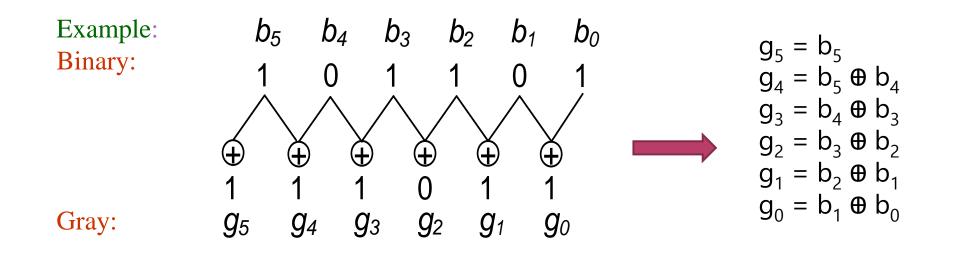

## Binary to Gray

# Gray to Binary

| Decimal | Gray  |       |       | <br>Binary |       |       |       |       |

|---------|-------|-------|-------|------------|-------|-------|-------|-------|

| number  | $g_3$ | $g_2$ | $g_1$ | $g_0$      | $b_3$ | $b_2$ | $b_1$ | $b_0$ |

| 0       | 0     | 0     | 0     | 0          | 0     | 0     | 0     | 0     |

| 1       | 0     | 0     | 0     | 1          | 0     | 0     | 0     | 1     |

| 2       | 0     | 0     | 1     | 1          | 0     | 0     | 1     | 0     |

| 3       | 0     | 0     | 1     | 0          | 0     | 0     | 1     | 1     |

| 4       | 0     | 1     | 1     | 0          | 0     | 1     | 0     | 0     |

| 5       | 0     | 1     | 1     | 1          | 0     | 1     | 0     | 1     |

| 6       | 0     | 1     | 0     | 1          | 0     | 1     | 1     | 0     |

| 7       | 0     | 1     | 0     | 0          | 0     | 1     | 1     | 1     |

| 8       | 1     | 1     | 0     | 0          | 1     | 0     | 0     | 0     |

| 9       | 1     | 1     | 0     | 1          | 1     | 0     | 0     | 1     |

| 10      | 1     | 1     | 1     | 1          | 1     | 0     | 1     | 0     |

| 11      | 1     | 1     | 1     | 0          | 1     | 0     | 1     | 1     |

| 12      | 1     | 0     | 1     | 0          | 1     | 1     | 0     | 0     |

| 13      | 1     | 0     | 1     | 1          | 1     | 1     | 0     | 1     |

| 14      | 1     | 0     | 0     | 1          | 1     | 1     | 1     | 0     |

| 15      | 1     | 0     | 0     | 0          | 1     | 1     | 1     | 1     |

$$b_{5} = g_{5}$$

$$b_{4} = g_{5} \oplus g_{4}$$

$$b_{3} = g_{5} \oplus g_{4} \oplus g_{3}$$

$$b_{2} = g_{5} \oplus g_{4} \oplus g_{3} \oplus g_{2}$$

$$b_{1} = g_{5} \oplus g_{4} \oplus g_{3} \oplus g_{2} \oplus g_{1}$$

$$b_{0} = g_{5} \oplus g_{4} \oplus g_{3} \oplus g_{2} \oplus g_{1} \oplus g_{0}$$

## **Reflection of Gray Codes**

| <br> <br>) |

|------------|

|            |

| ٦          |

| J          |

| )          |

| 1          |

| 1          |

| )          |

| )          |

| 1          |

| 1          |

| )          |

| )          |

| 1          |

| 1          |

|            |

000

1

#### So, called reflected code

## Alphanumeric Codes

- ► How do you handle alphanumeric data?

- ► Easy answer!

- ► Formulate a binary code to represent characters! ☺

- ► For the 26 letter of the alphabet would need 5 bit for representation.

- But what about the upper case and lower case, and the digits, and special characters

## ASCII

- ► ASCII stands for American Standard Code for Information Interchange

- ▶ The code uses 7 bits to encode 128 unique characters

- ▶ Formally, work to create this code began in 1960. 1<sup>st</sup> standard in 1963. Last updated in 1986

- Represents the numbers

- ► All start 011 xxxx and the xxxx is the BCD for the digit

- Represent the characters of the alphabet

- ▶ Start with either 100, 101, 110, or 111

- ► A few special characters are in this area

- ► Start with 010 space and !"#\$%&'()\*+.-,/

- ► Start with 000 or 001 control char like ESC

Table 1.7

American Standard Code for Information Interchange (ASCII)

.

|          |     |     |     | b7b6b5 |     |     |     | -   | NUL        | Null               |

|----------|-----|-----|-----|--------|-----|-----|-----|-----|------------|--------------------|

| b4b3b2b1 | 000 | 001 | 010 | 011    | 100 | 101 | 110 | 111 | SOH<br>STX | Start o<br>Start o |

| 0000     | NUL | DLE | SP  | 0      | @   | Р   | •   | р   | ETX        | End of             |

| 0001     | SOH | DC1 | !   | 1      | А   | Q   | а   | q   | EOT        | End of             |

| 0010     | STX | DC2 |     | 2      | В   | R   | b   | r   | ENQ        | Enqui              |

| 0011     | ETX | DC3 | #   | 3      | С   | S   | с   | S   | ACK        | Ackno              |

| 0100     | EOT | DC4 | \$  | 4      | D   | Т   | d   | t   | BEL        | Bell               |

| 0101     | ENQ | NAK | %   | 5      | E   | U   | e   | u   |            |                    |

| 0110     | ACK | SYN | &   | 6      | F   | v   | f   | v   | BS         | Backs              |

| 0111     | BEL | ETB | •   | 7      | G   | W   | g   | w   | HT         | Horizo             |

| 1000     | BS  | CAN | (   | 8      | Н   | x   | h   | x   | LF         | Line for           |

| 1001     | HT  | EM  | )   | 9      | 1   | Y   | i   | У   | VT         | Vertica            |

| 1010     | LF  | SUB | *   | :      | J   | Z   | j   | z   | FF         | Form               |

| 1011     | VT  | ESC | +   | ;      | K   | [   | k   | {   | CR         | Carria             |

| 1100     | FF  | FS  |     | <      | L   | ١   | 1   |     |            |                    |

| 1101     | CR  | GS  | _   | =      | Μ   | 1   | m   | }   | SO         | Shift o            |

| 1110     | SO  | RS  | 2   | >      | N   | ^   | n   | ~   | SI         | Shift i            |

| 1111     | SI  | US  | 1   | ?      | 0   | -   | о   | DEL | SP         | Space              |

**Control characters**

| ull                | DLE | Data-link escape          |

|--------------------|-----|---------------------------|

| art of heading     | DC1 | Device control 1          |

| art of text        | DC2 | Device control 2          |

| nd of text         | DC3 | Device control 3          |

| nd of transmission | DC4 | Device control 4          |

| nquiry             | NAK | Negative acknowledge      |

| cknowledge         | SYN | Synchronous idle          |

| ell                | ETB | End-of-transmission block |

| ackspace           | CAN | Cancel                    |

| orizontal tab      | EM  | End of medium             |

| ne feed            | SUB | Substitute                |

| ertical tab        | ESC | Escape                    |

| orm feed           | FS  | File separator            |

| arriage return     | GS  | Group separator           |

| ift out            | RS  | Record separator          |

| ift in             | US  | Unit separator            |

| bace               | DEL | Delete                    |

|                    |     |                           |

## **ASCII** Properties

ASCII has some interesting properties:

- Digits 0 to 9 span Hexadecimal values 30<sub>16</sub> to 39<sub>16</sub>

- Upper case A Z span  $41_{16}$  to  $5A_{16}$

- Lower case a z span  $61_{16}$  to  $7A_{16}$

• Lower to upper case translation (and vice versa) occurs by flipping bit 6.

- Delete (DEL) is all bits set, a carryover from when punched paper tape was used to store messages.

- Punching all holes in a row erased a mistake!

## Lecture of Module 2

#### **Logic Gates**

- Introduction

- Logical Operators

- **Basic Gates**

- Universal Gates

- **Realization of Basic Gates using Universal Gates**

- Other Logic Gates

## Introduction

- ▶ <u>Binary variables</u> take on one of two values

- ► <u>Logical operators</u> operate on binary values and binary variables

- ▶ Basic logical operators are the <u>logic functions</u> AND, OR and NOT

- ► <u>Logic gates</u> implement logic functions

- ► <u>Boolean Algebra</u>: a useful mathematical system for specifying and transforming logic functions

- We study Boolean algebra as a foundation for designing and analyzing digital systems

### **Binary Variables**

- Recall that the two binary values have different names:

- ► True/False

- ► On/Off

- ► Yes/No

- ► 1/0

- ▶ We use 1 and 0 to denote the two values.

- Variable identifier examples:

- ► A, B, x, y, z, or X<sub>1</sub>, X<sub>2</sub> etc. for now

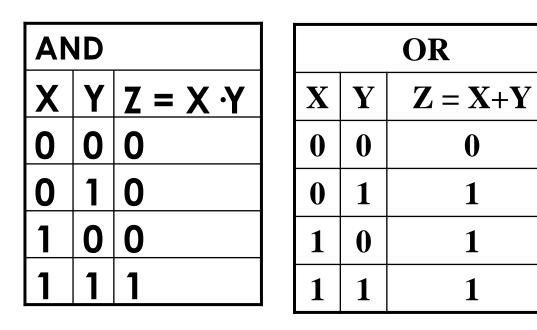

# **Logical Operations**

- ► The three basic logical operations are:

- ► AND

- ► OR

- ► NOT

- ► AND is denoted by a dot (•)

- OR is denoted by a plus (+)

- NOT is denoted by an over bar (<sup>-</sup>), a single quote mark (') after, or (~) before the variable

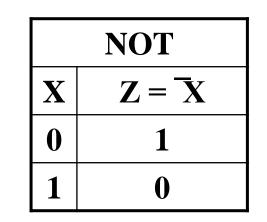

Operators operate on binary values and binary variablesOperations are defined on the values "0" and "1" for each operator:

| AND             | OR        | NOT          |

|-----------------|-----------|--------------|

| $0 \cdot 0 = 0$ | 0 + 0 = 0 | <b>0</b> = 1 |

| $0 \cdot 1 = 0$ | 0 + 1 = 1 | <b>1</b> = 0 |

| $1 \cdot 0 = 0$ | 1 + 0 = 1 |              |

| $1 \cdot 1 = 1$ | 1 + 1 = 1 |              |

#### **Truth Tables**

- Truth table a tabular listing of the values of a function for all possible combinations of values on its arguments

- Example: Truth tables for the basic logic operations:

#### **Logic Function Implementation**

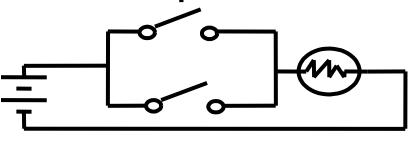

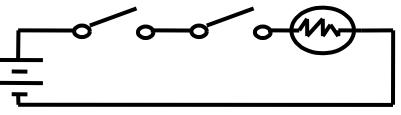

- Using Switches

- **For inputs:**

- ▶ logic 1 is switch closed

- ▶ logic 0 is <u>switch open</u>

- **For outputs:**

- ▶ logic 1 is <u>light on</u>

- ▶ logic 0 is <u>light off</u>.

Switches in parallel => OR

Switches in series => AND

## Logic Gates

- In the earliest computers, switches were opened and closed by magnetic fields produced by energizing coils in *relays*. The switches in turn opened and closed the current paths.

- Later, vacuum tubes that open and close current paths electronically replaced relays.

- Today, *transistors* are used as electronic switches that open and close current paths.

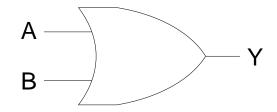

- ► NOT, AND and OR Gates (Basic gates)

- NAND and NOR Gates (Universal logic gates)

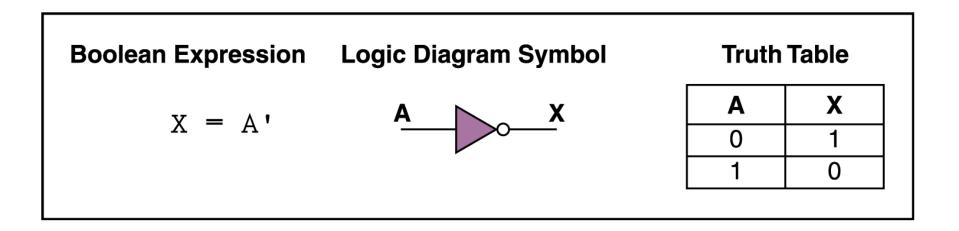

A NOT gate accepts one input signal (0 or 1) and returns the opposite signal as output

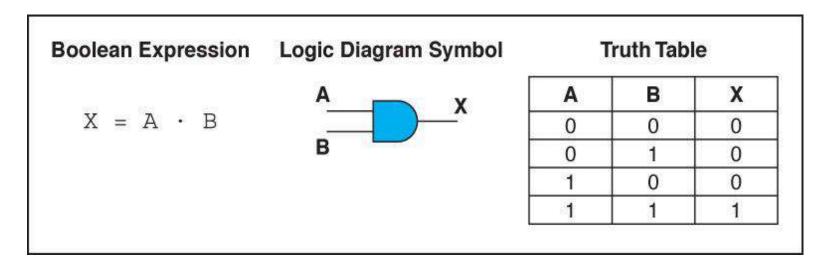

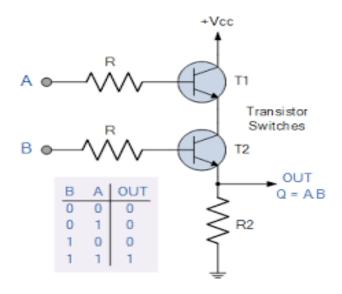

### AND Gate

If all inputs are 1, the output is 1; otherwise, the output is 0 Or if any input is 0, output is 0

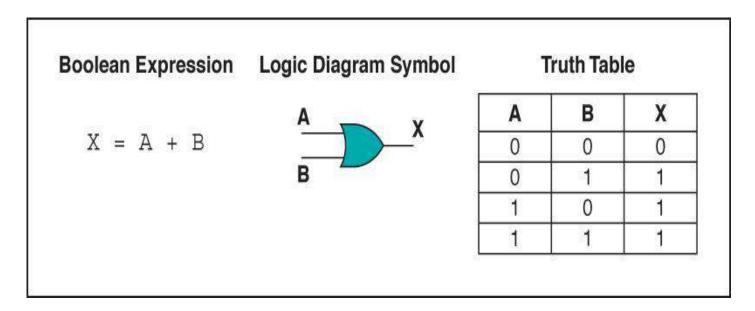

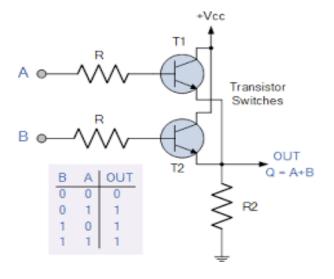

### OR Gate

If all inputs are 0, the output is 0; otherwise, the output is 1 Or if any input is 1, output will be 1

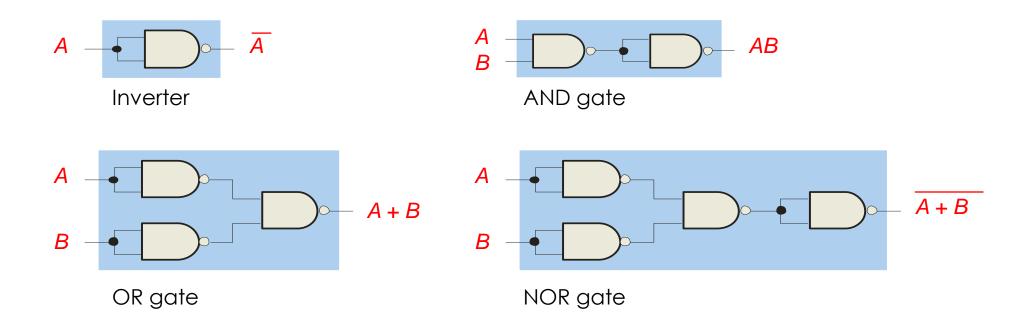

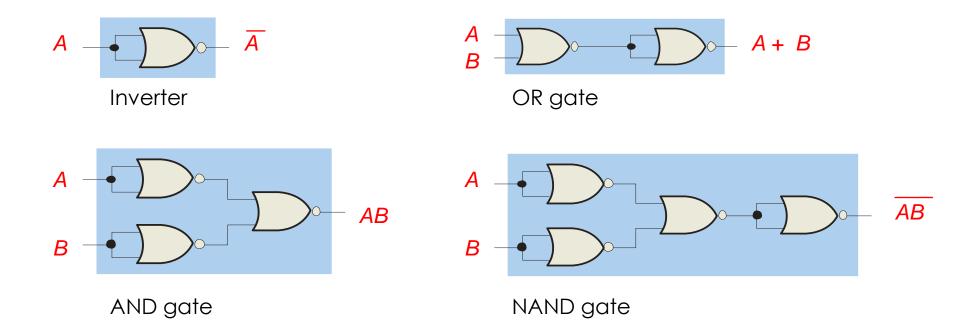

### Universal Gates

- Universal Logic Gate: Any basic gate or logic function can be realized using this gate

- □ Two universal logic gates

- ✤ NAND

- ✤ NOR

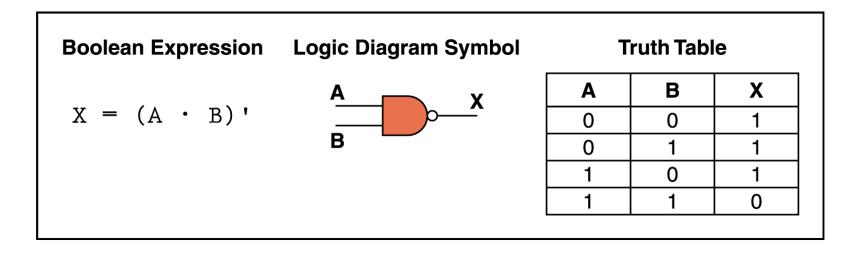

#### NAND Gate

#### If all inputs are 1, the output is 0; otherwise, the output is 1

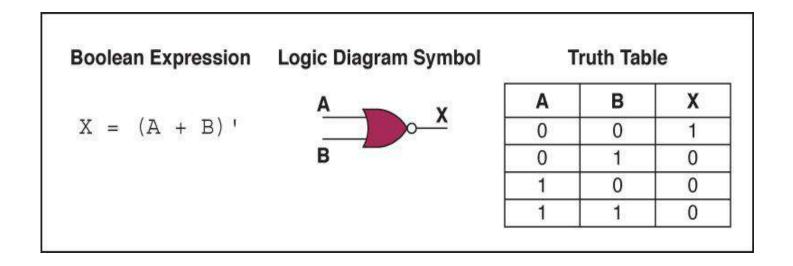

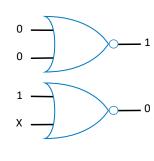

### NOR Gate

#### If all inputs are 0, the output is 1; otherwise, the output is 0

**NAND** gates are sometimes called **universal** gates because they can be used to produce the other basic Boolean functions.

NOR gates are also universal gates and can form all of the basic gates.

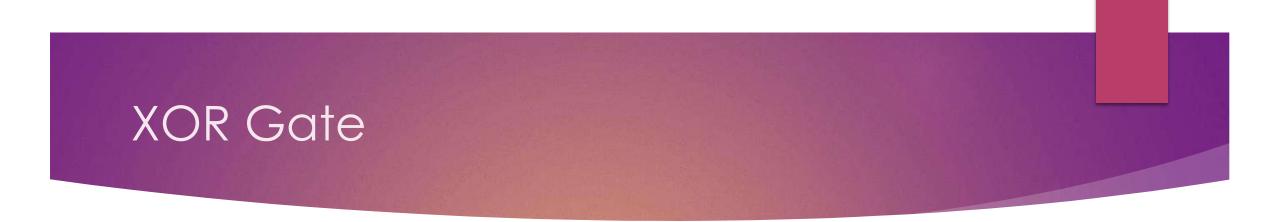

If odd numbers of inputs are 1, the output is 1; otherwise, the output is 0

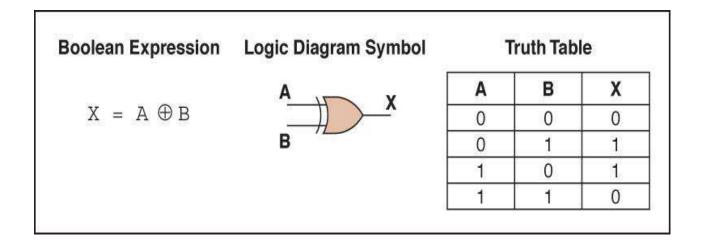

## X-NOR Gate

| X | Y | Z |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

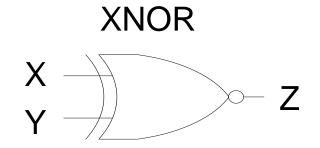

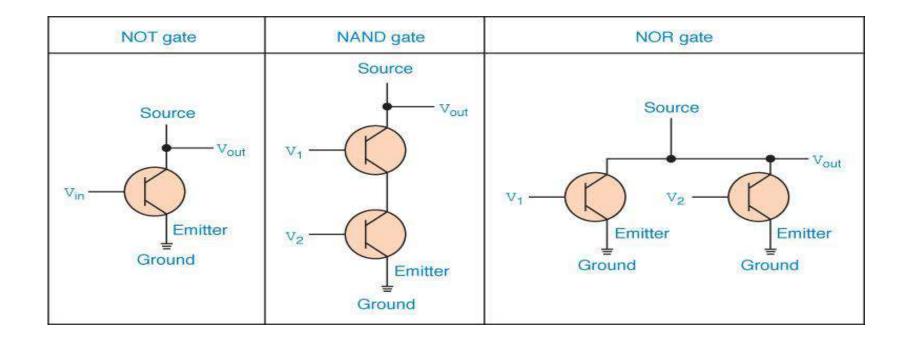

## Constructing Gates

#### **Transistor**

A device that acts either as a wire that conducts electricity or as a resistor that blocks the flow of electricity, depending on the voltage level of an input signal

A transistor has no moving parts, yet acts like a switch

It is made of a semiconductor material, which is neither a particularly good conductor of electricity nor a particularly good insulator

| A transistor has three terminals                                                                                                                 |

|--------------------------------------------------------------------------------------------------------------------------------------------------|

| A source                                                                                                                                         |

| A base                                                                                                                                           |

| An emitter, typically connected to a ground wire                                                                                                 |

| If the electrical signal is grounded, it is allowed to flow through<br>an alternative route to the ground (literally) where it can do<br>no harm |

AND Gate

#### OR Gate

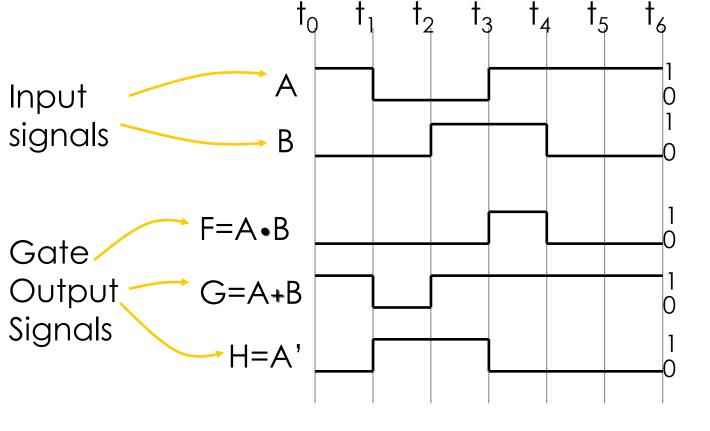

## Timing Diagram

Transitions

<u>Basic</u> <u>Assumption:</u> Zero time for signals to propagate Through gates

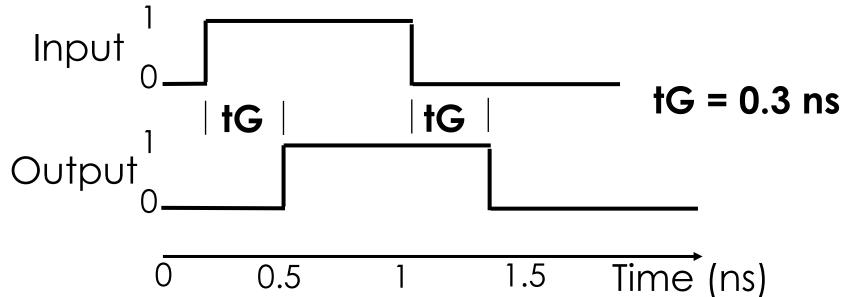

## Gate Delay

- In actual physical gates, if one or more input changes causes the output to change, the output change does not occur instantaneously.

- The delay between an input change(s) and the resulting output change is the gate delay denoted by t<sub>G</sub>:

#### **Boolean Algebra**

- Introduction

- Boolean Algebra

- Properties

- Algebraic Manipulation

- De-Morgan Theorem

- Complementation

- ► Truth Table

## Introduction

- Understand the relationship between Boolean logic and digital computer circuits.

- ► Learn how to design simple logic circuits.

- Understand how digital circuits work together to form complex computer systems.

- In the latter part of the nineteenth century, George Boole suggested that logical thought could be represented through mathematical equations.

- Computers, as we know them today, are implementations of Boole's *Laws of Thought*.

- In this chapter, you will learn the simplicity that constitutes the essence of the machine (Boolean Algebra).

#### Boolean algebra

Boolean algebra is a mathematical system for the manipulation of variables that can have one of two values.

- ▶ In formal logic, these values are "true" and "false."

- In digital systems, these values are "on" and "off," 1 and 0, or "high" and "low."

- Boolean expressions are created by performing operations on Boolean variables.

- Common Boolean operators include AND, OR, NOT, XOR, NAND and NOR

- ► A Boolean operator can be completely described using a truth table.

- The truth table for the Boolean operators AND, OR and NOT are shown at the right.

- ▶ The AND operator is also known as a Boolean product.

- ► The OR operator is the Boolean sum.

- ► The NOT operation is most often designated by an over-bar. It is sometimes indicated by a prime mark ( ' ) or an "elbow" (¬).

| X AND Y |   |    |  |  |

|---------|---|----|--|--|

| x       | Y | XY |  |  |

| 0       | 0 | 0  |  |  |

| 0       | 1 | 0  |  |  |

| 1       | 0 | 0  |  |  |

| 1       | 1 | 1  |  |  |

| ζ |

|---|

|   |

|   |

|   |

|   |

|   |

| NOT X                   |  |  |  |  |

|-------------------------|--|--|--|--|

| $\overline{\mathbf{x}}$ |  |  |  |  |

| 1<br>0                  |  |  |  |  |

|                         |  |  |  |  |

- ► A Boolean function has:

- At least one Boolean variable,

- At least one Boolean operator, and

- At least one input from the set {0,1}

- ▶ It produces an output that is also a member of the set {0,1}

Now you know why the binary numbering system is so handy in digital systems

- Digital computers contain circuits that implement Boolean functions.

- The simpler that we can make a Boolean function, the smaller the circuit that will result.

- Simpler circuits are cheaper to build, consume less power, and run faster than complex circuits.

- With this in mind, we always want to reduce our Boolean functions to their simplest form.

- ▶ There are a number of Boolean identities that help us to do this.

## Properties of Boolean Algebra

Most Boolean identities have an AND (product) form as well as an OR (sum) form.

| Identity                                                  | AND                                            | OR                                                         |

|-----------------------------------------------------------|------------------------------------------------|------------------------------------------------------------|

| Name                                                      | Form                                           | Form                                                       |

| Identity Law<br>Null Law<br>Idempotent Law<br>Inverse Law | $1x = x$ $0x = 0$ $xx = x$ $x\overline{x} = 0$ | $0 + x = x$ $1 + x = 1$ $x + x = x$ $x + \overline{x} = 1$ |

Our second group of Boolean identities should be familiar to you from your study of algebra:

| Identity         | AND                | OR                  |

|------------------|--------------------|---------------------|

| Name             | Form               | Form                |

| Commutative Law  | xy = yx            | x+y = y+x           |

| Associative Law  | (xy) z = x (yz)    | (x+y)+z = x + (y+z) |

| Distributive Law | x+yz = (x+y) (x+z) | x (y+z) = xy+xz     |

▶ Our last group of Boolean identities are perhaps the most useful.

▶ If you have studied set theory or formal logic, these laws are also familiar to you.

| Identity<br>Name                 | AND<br>Form                                       | OR<br>Form |  |

|----------------------------------|---------------------------------------------------|------------|--|

| Absorption Law<br>DeMorgan's Law |                                                   |            |  |

| Double<br>Complement Law         | $\overline{(\overline{\mathbf{x}})} = \mathbf{x}$ |            |  |

▶ We can use Boolean identities to simplify the function:

$F(X,Y,Z) = (X + Y) (X + \overline{Y}) (\overline{X\overline{Z}})$

as follows:

| $(X + Y) (X + \overline{Y}) (\overline{X\overline{Z}})$ $(X + Y) (X + \overline{Y}) (\overline{X} + Z)$ $(XX + X\overline{Y} + XY + Y\overline{Y}) (\overline{X} + Z)$ | Idempotent Law (Rewriting)<br>DeMorgan's Law<br>Distributive Law |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|

| $((X + Y\overline{Y}) + X(Y + \overline{Y}))(\overline{X} + Z)$ $((X + 0) + X(1))(\overline{X} + Z)$                                                                   | Commutative & Distributive Laws<br>Inverse Law                   |

| $\frac{X(X + Z)}{XX + XZ}$                                                                                                                                             | Idempotent Law<br>Distributive Law                               |

| 0 + XZ<br>XZ                                                                                                                                                           | Inverse Law<br>Idempotent Law                                    |

# With respect to duality, Identities 1 – 8 have the following relationship:

- 1. X + 0 = X 2.  $X \cdot 1 = X$  (dual of 1)

- 3. X + 1 = 1 4.  $X \cdot 0 = 0$  (dual of 3)

- 5. X + X = X 6.  $X \cdot X = X$  (dual of 5)

- 7. X + X' = 1 8.  $X \cdot X' = 0$  (dual of 8)

## Algebraic Manipulation

- **Boolean algebra is a useful tool for simplifying digital circuits.**

- **Why do it? Simpler can mean cheaper, smaller, faster.**

► Example: Prove x'y'z' + x'yz' + xyz' = x'z' + yz'

## Complementation

- Sometimes it is more economical to build a circuit using the complement of a function (and complementing its result) than it is to implement the function directly.

- DeMorgan's law provides an easy way of finding the complement of a Boolean function.

- DeMorgan's law states:

$$(\overline{xy}) = \overline{x} + \overline{y}$$

and  $(\overline{x+y}) = \overline{xy}$

Find the complement of F(x, y, z) = x y' z' + x' y z

Note: The complement of a function can also be derived by finding the function's *dual*, and then complementing all of the literals

## Truth Table

- Enumerates all possible combinations of variable values and the corresponding function value

- Fruth tables for some arbitrary functions  $F_1(x,y,z)$ ,  $F_2(x,y,z)$ , and  $F_3(x,y,z)$  are shown to the right.

- ► Truth table: a <u>unique</u> representation of a Boolean function

- If two functions have identical truth tables, the functions are equivalent (and vice-versa).

- ▶ Truth tables can be used to prove equality theorems.

- However, the size of a truth table grows <u>exponentially</u> with the number of variables involved. This motivates the use of Boolean Algebra.

| × | У | Z | $F_1$ | F <sub>2</sub> | $F_3$ |

|---|---|---|-------|----------------|-------|

| 0 | 0 | 0 | 0     | 1              | 1     |

| 0 | 0 | 1 | 0     | 0              | 1     |

| 0 | 1 | 0 | 0     | 0              | 1     |

| 0 | 1 | 1 | 0     | 1              | 1     |

| 1 | 0 | 0 | 0     | 1              | 0     |

| 1 | 0 | 1 | 0     | 1              | 0     |

| 1 | 1 | 0 | 0     | 0              | 0     |

| 1 | 1 | 1 | 1     | 0              | 1     |

#### **Standard SOP and POS**

- ▶ Introduction

- ► SOP and POS

- Minterms and Maxterms

- Canonical Forms

- Conversion Between Canonical Forms

- Standard Forms

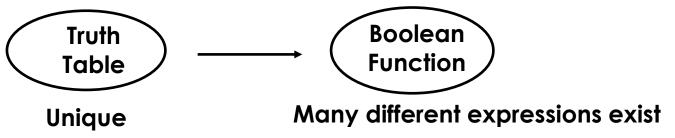

## Introduction

- Through our exercises in simplifying Boolean expressions, we see that there are numerous ways of stating the same Boolean expression.

- These "synonymous" forms are *logically equivalent*.

- ► Logically equivalent expressions have identical truth tables.

- ► In order to eliminate as much confusion as possible, designers express Boolean functions in *standardized* or *canonical* form.

## SOP and POS

- There are two canonical forms for Boolean expressions: Sum-Of-Products (SOP) and Product-Of-Sums (POS).

- Recall the Boolean product is the AND operation and the Boolean sum is the OR operation.

▶ In the Sum-Of-Products form, ANDed variables are ORed together.

For example: F(x, y, z) = xy + xz + yz

In the Product-Of-Sums form, ORed variables are ANDed together:

For example: F(x,y,z) = (x+y) (x+z) (y+z)

## Definitions

- *Literal:* A variable or its complement

- Product term: literals connected by •

- Sum term: literals connected by +

- Minterm: a product term in which all the variables appear exactly once, either complemented or un-complemented

- Maxterm: a sum term in which all the variables appear exactly once, either complemented or un-complemented

#### Truth Table notation for Minterms and Maxterms

- Minterms and Maxterms are easy to denote using a truth table.

- Example: Assume 3 variables x,y,z (order is fixed)

- Any Boolean function F() can be expressed as a unique sum of minterms and a unique product of maxterms (under a fixed variable ordering).

- In other words, every function F() has two canonical forms:

- Canonical Sum-Of-Products (sum of minterms)

- Canonical Product-Of-Sums (product of maxterms)

| × | У | z | Minterm                 | Maxterm                   |

|---|---|---|-------------------------|---------------------------|

| 0 | 0 | 0 | x'y'z' = m <sub>o</sub> | $x+y+z = M_0$             |

| 0 | 0 | 1 | $x'y'z = m_1$           | $x+y+z' = M_1$            |

| 0 | 1 | 0 | x'yz' = m <sub>2</sub>  | x+y'+z = M <sub>2</sub>   |

| 0 | 1 | 1 | x'yz = m <sub>3</sub>   | x+y'+z'= M <sub>3</sub>   |

| 1 | 0 | 0 | $xy'z' = m_4$           | x'+y+z = M <sub>4</sub>   |

| 1 | 0 | 1 | xy'z = m <sub>5</sub>   | x'+y+z' = M <sub>5</sub>  |

| 1 | 1 | 0 | $xyz' = m_6$            | $x'+y'+z = M_6$           |

| 1 | 1 | 1 | xyz = m <sub>7</sub>    | x'+y'+z' = M <sub>7</sub> |

## Canonical Forms

- Canonical Sum-Of-Products: The minterms included are those m<sub>j</sub> such that F() = 1 in row j of the truth table for F().

- Canonical Product-Of-Sums: The maxterms included are those M<sub>i</sub> such that F() = 0 in row j of the truth table for F().

- $f_1(a,b,c) = \sum m(1,2,4,6)$ , where  $\sum$  indicates that this is a sum-of-products form, and m(1,2,4,6) indicates that the minterms to be included are  $m_1$ ,  $m_2$ ,  $m_4$ , and  $m_6$ .

- $f_1(a,b,c) = \prod M(0,3,5,7)$ , where  $\prod$  indicates that this is a product-of-sums form, and M(0,3,5,7) indicates that the maxterms to be included are M<sub>0</sub>, M<sub>3</sub>, M<sub>5</sub>, and M<sub>7</sub>.

- Since  $m_j = M_j$ ' for any j,  $\sum m(1,2,4,6) = \prod M(0,3,5,7) = f_1(a,b,c)$

## **Conversion Between Canonical Forms**

▶ Replace ∑ with ∏ (or *vice versa*) and replace those *j* 's that appeared in the original form with those that do not.

```

• Example:

f_1(a,b,c) = a'b'c + a'bc' + ab'c' + abc'

= m_1 + m_2 + m_4 + m_6

= \sum(1,2,4,6)

= \prod(0,3,5,7)

= (a+b+c)\bullet(a+b'+c')\bullet(a'+b+c')\bullet(a'+b'+c')

```

$$F = \overline{X}\overline{Y}\overline{Z} + \overline{X}Y\overline{Z} + X\overline{Y}\overline{Z} + XY\overline{Z} = m_0 + m_2 + m_5 + m_7 = \sum m(0, 2, 5, 7)$$

$$\overline{F} = \overline{X}\overline{Y}\overline{Z} + \overline{X}Y\overline{Z} + X\overline{Y}\overline{Z} + XY\overline{Z} = m_1 + m_3 + m_4 + m_6 = \sum m(1, 3, 4, 6)$$

$$\overline{F} = m_1 + m_3 + m_4 + m_6$$

$$\Rightarrow F = \overline{m_1 + m_3 + m_4 + m_6} = \overline{m_1} \cdot \overline{m_3} \cdot \overline{m_4} \cdot \overline{m_6}$$

$$\Rightarrow F = M_1 \cdot M_3 \cdot M_4 \cdot M_6 = (X + Y + \overline{Z})(X + \overline{Y} + \overline{Z})(\overline{X} + Y + Z)(\overline{X} + \overline{Y} + Z)$$

$$= \prod M(1, 3, 4, 6)$$

#### **Standard Forms**

- Standard forms are "*like*" canonical forms, except that not all variables need appear in the individual product (SOP) or sum (POS) terms.

- Example:

f<sub>1</sub>(a,b,c) = a'b'c + bc' + ac'

is a *standard* sum-of-products form

- f<sub>1</sub>(a,b,c) = (a+b+c)•(b'+c')•(a'+c')

is a *standard* product-of-sums form.

#### Conversion of SOP from standard to canonical form

- Expand non-canonical terms by inserting equivalent of 1 in each missing variable x: (x + x') = 1

- Remove duplicate minterms

#### Conversion of POS from standard to canonical form

- Expand non-canonical terms by adding 0 in terms of missing variables (e.g., xx' = 0) and using the distributive law

- Remove duplicate maxterms

$$f_1(a,b,c) = (a+b+c) \cdot (b'+c') \cdot (a'+c') = (a+b+c) \cdot (aa'+b'+c') \cdot (a'+bb'+c') = (a+b+c) \cdot (a+b'+c') \cdot (a'+b'+c') \cdot (a'+b+c') \cdot (a'+b'+c') = (a+b+c) \cdot (a+b'+c') \cdot (a'+b'+c') \cdot (a'+b+c')$$

#### **Minimization Techniques**

### Overview

- Introduction

- Karnaugh Map (K-Map)

- Simplification Rules

- K-Map Simplification for Two Variables

- ► K-Map Simplification for Three Variables

- K-Map Simplification for Four Variables

- Don't Care Conditions

- Redundancy

- Design of Combinational Circuits

Simplification from Boolean function

- Finding an equivalent expression that is least expensive to implement

- For a simple function, it is possible to obtain a simple expression for low cost implementation

- But, with complex functions, it is a very difficult for implementation

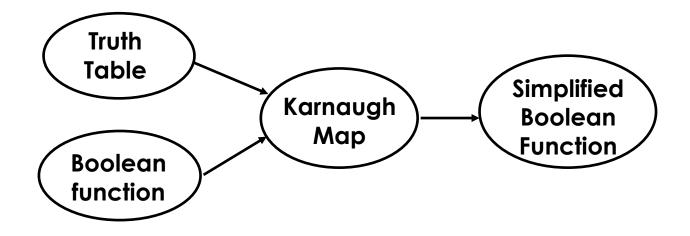

Karnaugh Map (K-map) is a simple procedure for simplification of Boolean expressions.

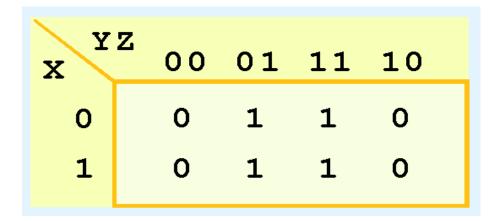

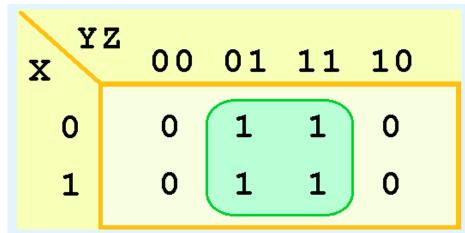

## Karnaugh Map (K-Map)

- Karnaugh maps (K-maps) are graphical representations of Boolean functions.

- One *map cell* corresponds to a row in the truth table.

- ▶ Also, one map cell corresponds to a minterm or a maxterm in the Boolean expression

- Each term is identified by a decimal number whose binary representation is identical to the binary interpretation of the input values of the term.

|      | C'D' | C'D | CD | CD' |

|------|------|-----|----|-----|

| Α'Β' | 0    | 1   | 3  | 2   |

| A'B  | 4    | 5   | 7  | 6   |

| АВ   | 12   | 13  | 15 | 14  |

| AB'  | 8    | 9   | 11 | 10  |

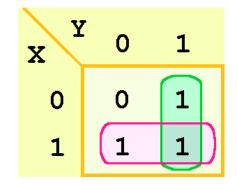

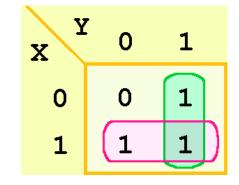

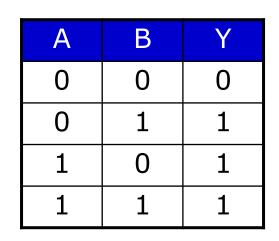

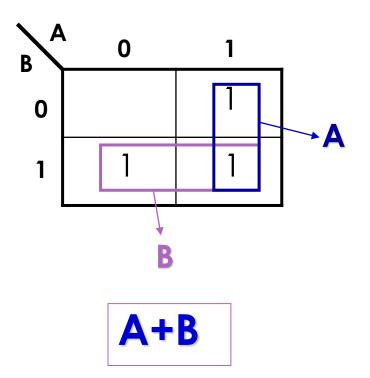

## K-Map Simplification for Two Variables

Of course, the Minterm function that we derived from our Truth Table was not in simplest terms.

▶ That's what we started with in this example.

We can, however, reduce our complicated expression to its simplest terms by finding adjacent 1s in the K-map that can be collected into groups that are powers of two.

• In our example, we have two such groups.

- Can you find them?

| Y<br>X | 0 | 1 |

|--------|---|---|

| 0      | 0 | 1 |

| 1      | 1 | 1 |

## K-Map Rules

The rules of K-map simplification are:

- Groupings can contain only 1s; no 0s.

- The number of 1s in a group must be a power of 2 even if it contains a single 1.

- Nearby 1s are to be grouped.

- Corner 1s are to be grouped.

- Group that wraps around the sides of a K-map.

- Diagonal groups are not allowed.

- The groups must be made as large as possible.

- Groups can overlap.

### K-Map Rules

- The best way of selecting two groups of 1s form our simple Kmap is shown.

- We see that both groups are powers of two and that the groups overlap.

## K-Map Simplification for Two Variables

2-variable Karnaugh maps are trivial but can be used to introduce the methods you need to learn. The map for a 2-input OR gate looks like this:

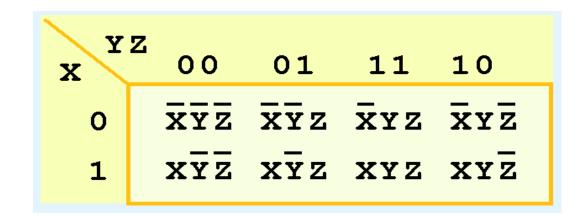

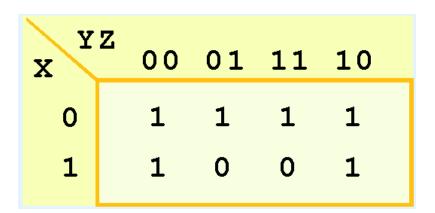

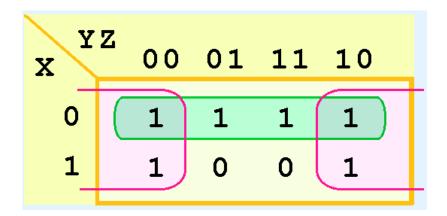

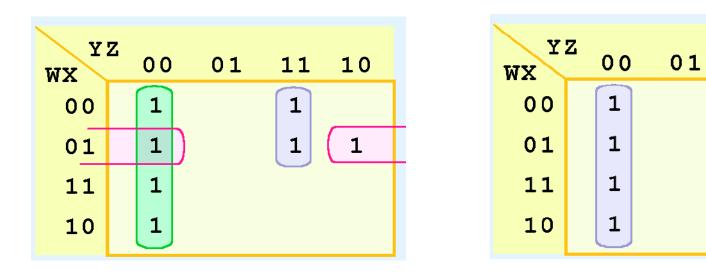

### K-Map Simplification for Three Variables

- ► A K-map for three variables is constructed as shown in the diagram below.

- ▶ We have placed each Minterm in the cell that will hold its value.

- Notice that the values for the yz combination at the top of the matrix form a pattern that is not a normal binary sequence.

#### Consider the function:

F(X, Y, Z) = X'Y'Z + X'YZ + XY'Z + XYZ

▶ Its K-map is given below.

▶ What is the largest group of 1s that is a power of 2?

- This grouping tells us that changes in the variables x and y have no influence upon the value of the function: They are irrelevant.

- This means that the function, F (X, Y, Z) = X'Y'Z + X'YZ + XY'Z + XYZ reduces to F = Z.

You could verify this reduction with Boolean Algebra

#### Now for a more complicated K-map. Consider the function: $F(X, Y, Z) = \overline{XYZ} + \overline{XYZ} + \overline{XYZ} + \overline{XYZ} + \overline{XYZ} + \overline{XYZ} + \overline{XYZ}$

▶ Its K-map is shown below. There are (only) two groupings of 1s.

Can you find them?

In this K-map, we see an example of a group that wraps around the sides of a K-map.

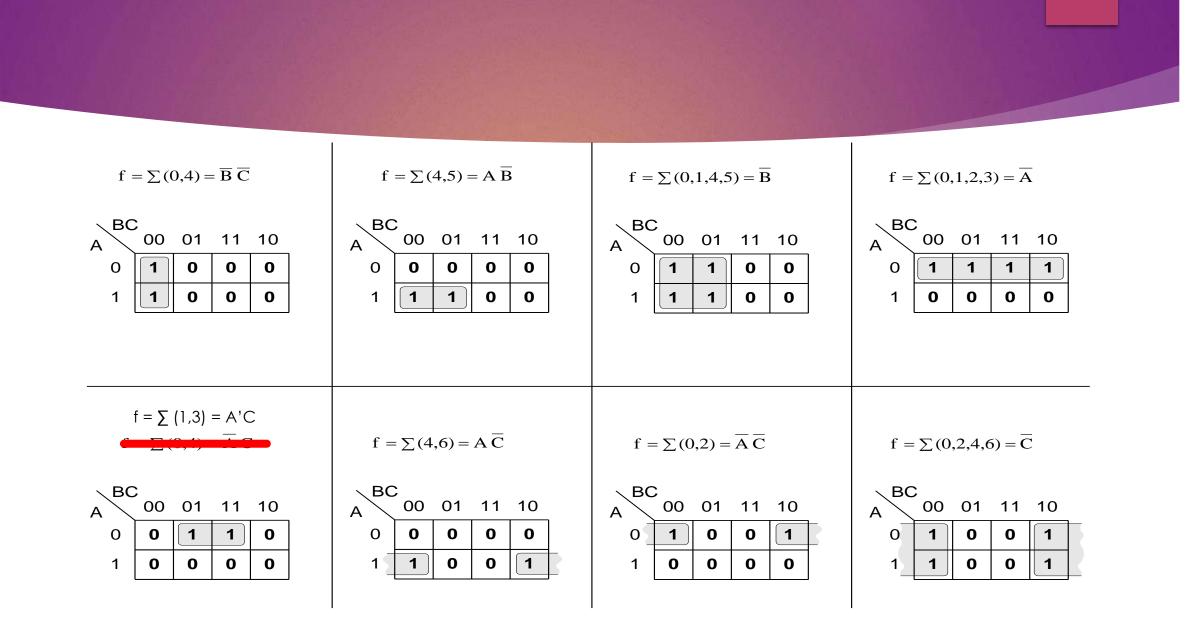

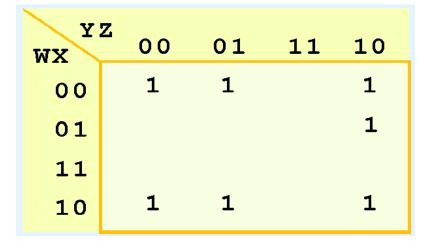

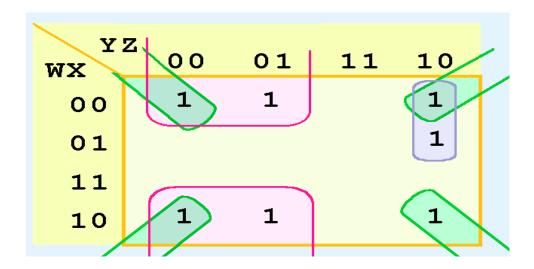

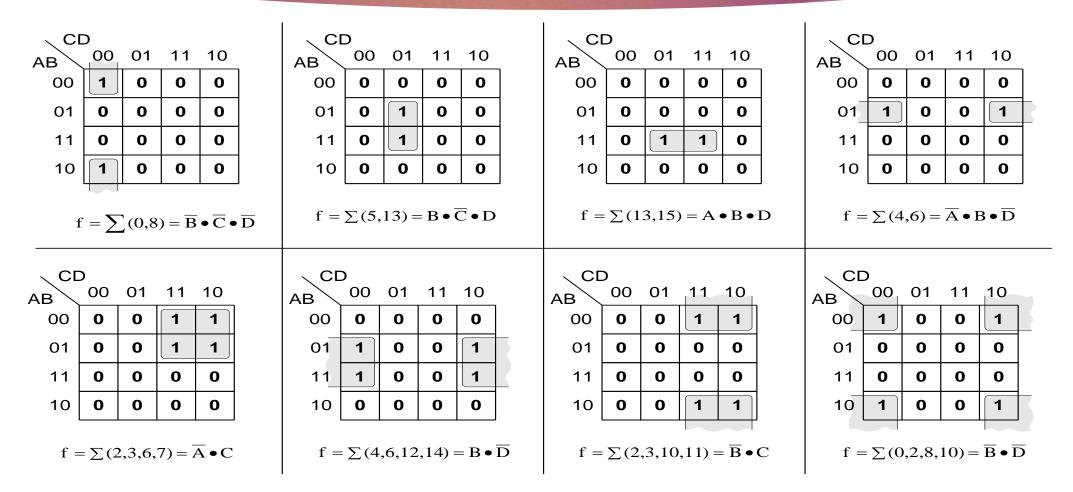

#### K-Map Simplification for Four Variables

- The K-map can be extended to accommodate the 16 Minterms that are produced by a four-input function.

- ▶ This is the format for a 16-minterm K-map.

| Y<br>WX | z<br>00     | 01           | 11                        | 10               |

|---------|-------------|--------------|---------------------------|------------------|

| 00      | <b>WXYZ</b> | <b>w</b> xyz | <b>.</b><br>w <b>x</b> yz | <b>w</b> xyz     |

| 01      | <b>WXYZ</b> | <b>w</b> xyz | WXYZ                      | <b>.</b><br>wxyz |

| 11      | wxyź        | WXYZ         | WXYZ                      | wxyz             |

| 10      | WXYZ        | wxyz         | wxyz                      | wxyz             |

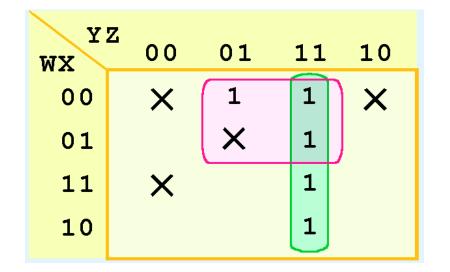

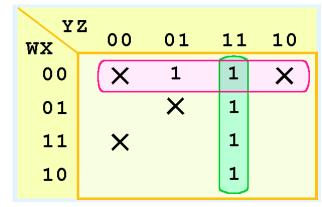

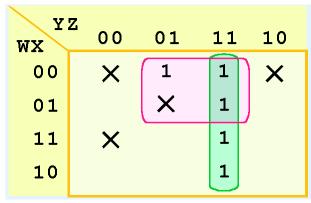

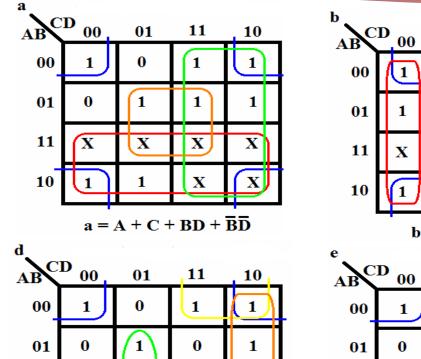

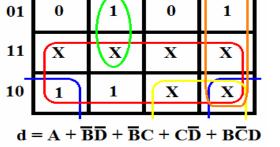

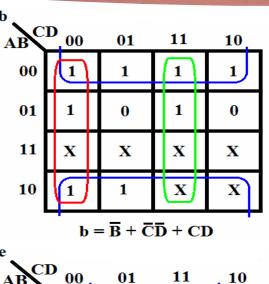

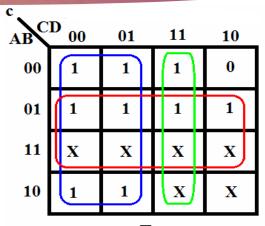

► We have populated the K-map shown below with the nonzero minterms from the function:

# $F(W, X, Y, Z) = \overline{W}\overline{X}\overline{Y}\overline{Z} + \overline{W}\overline{X}\overline{Y}Z + \overline{W}\overline{X}Y\overline{Z}$ $+ \overline{W}XY\overline{Z} + W\overline{X}\overline{Y}\overline{Z} + W\overline{X}\overline{Y}Z + W\overline{X}Y\overline{Z}$

Can you identify (only) three groups in this K-map?

- Our three groups consist of:

- ► A purple group entirely within the K-map at the right.

- ► A pink group that wraps the top and bottom.

- ► A green group that spans the corners.

- ▶ Thus we have three terms in our final function:

- It is possible to have a choice as to how to pick groups within a K-map, while keeping the groups as large as possible.

- The (different) functions that result from the groupings below are logically equivalent.

| СГ<br>АВ     | 00   | 01    | 11     | 10    |              | D    | 01    | 11   | 10  | AB |   | 01 | 11 | 10         | 7     |                      | D<br>00 | 01 | 11 | 10 |       |

|--------------|------|-------|--------|-------|--------------|------|-------|------|-----|----|---|----|----|------------|-------|----------------------|---------|----|----|----|-------|

| 00           | 0    | 0     | 0      | 0     | 00           | 0    | 0     | 1    | 0   | 00 | 1 | ο  | 1  | ) <b>O</b> |       | 00                   | 0       | 1  | 0  | 1  |       |

| 01           | 1    | 1     | 1      | 1     | 01           | 0    | 0     | 1    | 0   | 01 | 0 | 1  | Ο  | 1          |       | 01                   | 1       | 0  | 1  | 0  |       |

| 11           | 0    | 0     | 0      | 0     | 11           | 0    | 0     | 1    | 0   | 11 | 1 | Ο  | 1  | 0          | ]     | 11                   | 0       | 1  | 0  | 1  |       |

| 10           | 0    | 0     | 0      | 0     | 10           | 0    | 0     | 1    | 0   | 10 | 0 | 1  | 0  | 1          | ]     | 10                   | 1       | 0  | 1  | 0  | ]     |

| $f = \Sigma$ | (4,5 | 5,6,7 | 7) = 2 | Ā ● B | $f = \Sigma$ | (3,7 | ,11,1 | 5) = | C∙D |    |   |    |    |            | 2,15) | $f = \Sigma$ $f = A$ |         |    |    |    | 8,14) |

| CD<br>AB     |      | 01    | 11     | 10    |              |      | 01    | 11   | 10  | СС |   | 01 | 11 | 10         |       | СС                   |         | 01 | 11 | 10 |       |

| 00           | 0    | 1     | 1      | 0     | 00           | 1    | 0     | 0    | 1   | 00 | 0 | 0  | 0  | 0          |       | 00                   | 1       | 1  | 1  | 1  |       |

| 01           | 0    | 1     | 1      | 0     | 01           | 1    | 0     | 0    | 1   | 01 | 1 | 1  | 1  | 1          |       | 01                   | 0       | 0  | 0  | 0  |       |

| 11           | 0    | 1     | 1      | 0     | 11           | 1    | 0     | 0    | 1   | 11 | 1 | 1  | 1  | 1          |       | 11                   | 0       | 0  | 0  | 0  |       |

| 10           | 0    | 1     | 1      | 0     | 10           | 1    | 0     | 0    | 1   | 10 | 0 | 0  | 0  | 0          |       | 10                   | 1       | 1  | 1  | 1  |       |

|              |      |       |        |       |              |      |       |      |     |    |   |    |    |            |       |                      |         |    |    |    |       |

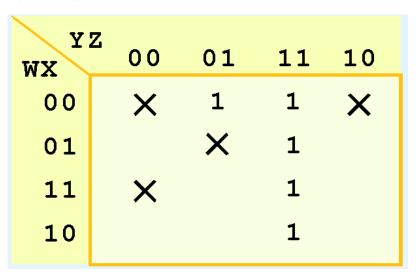

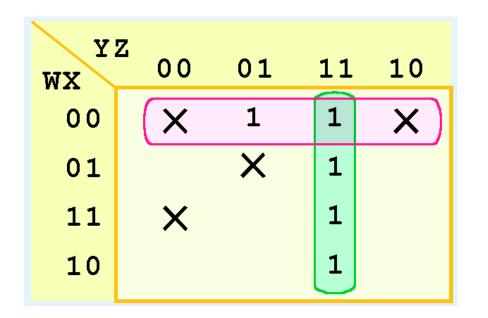

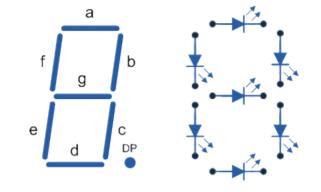

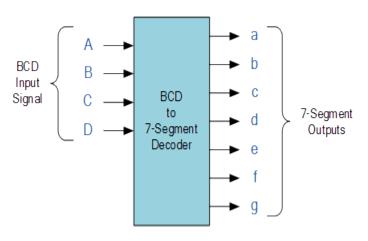

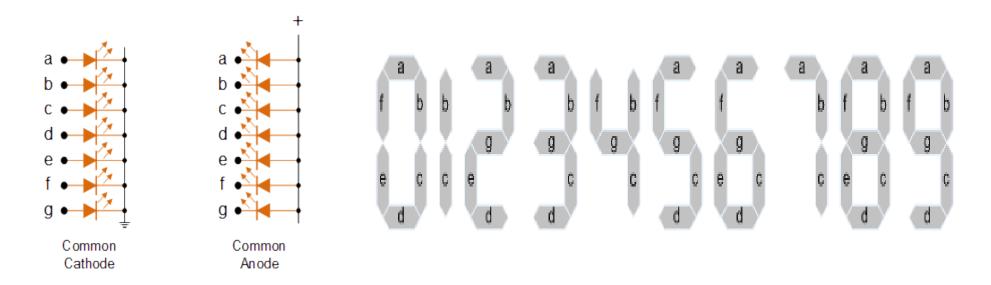

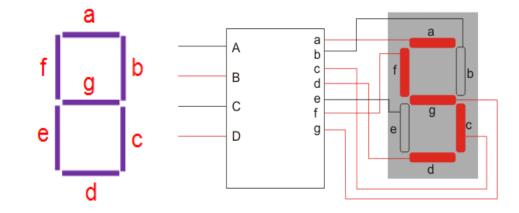

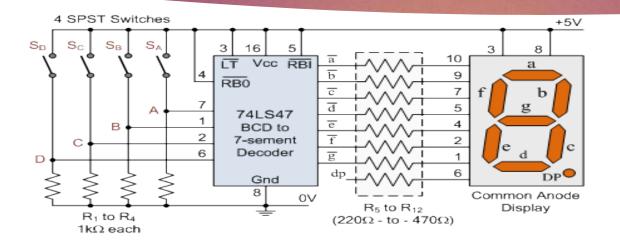

#### Don't Care Conditions

- Real circuits don't always need to have an output defined for every possible input.

- For example, some calculator displays consist of 7-segment LEDs. These LEDs can display 2<sup>7</sup> patterns but all patterns are not used.

- If a circuit is designed so that a particular set of inputs can never happen, we call this set of inputs a *don't care* condition.

- ▶ They are very helpful to us in K-map circuit simplification.

- In a K-map, a don't care condition is identified by an X in the cell of the minterm(s) for the don't care inputs, as shown below.

- In performing the simplification, we are free to include or ignore the X's when creating our groups.

## In one grouping in the K-map below, we have the function: F = W'X' + YZ

► A different grouping gives us the function:

F(W,X,Y,Z) = WZ + YZ

► The truth table of:

F(W, X, Y, Z) = W'X' + YZdiffers from the truth table of:

F(W, X, Y, Z) = WZ + YZ

However, the values for which they differ, are the inputs for which we have don't care conditions.

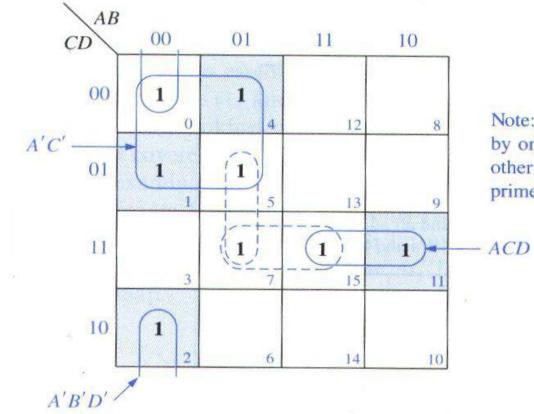

#### Redundancy

Note: 1's shaded in blue are covered by only one prime implicant. All other 1's are covered by at least two prime implicants.

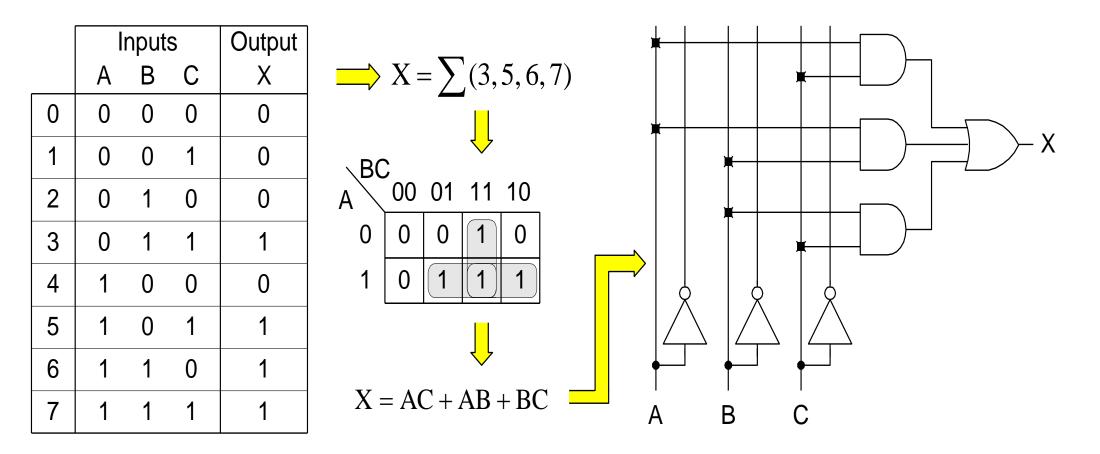

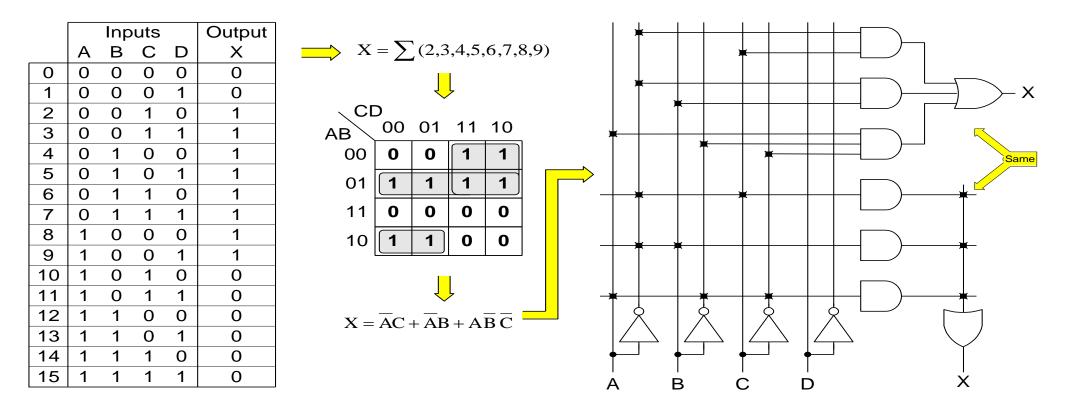

#### Design of combinational digital circuits

- Steps to design a combinational digital circuit:

- From the problem statement derive the truth table

- From the truth table derive the unsimplified logic expression

- Simplify the logic expression

- ▶ From the simplified expression draw the logic circuit

- Example: Design a 3-input (A,B,C) digital circuit that will give at its output (X) a logic 1 only if the binary number formed at the input has more ones than zeros.

Example: Design a 4-input (A,B,C,D) digital circuit that will give at its output (X) a logic 1 only if the binary number formed at the input is between 2 and 9 (including).

## Conclusion

- K-maps provide an easy graphical method of simplifying Boolean expressions.

- A K-map is a matrix consisting of the outputs of the minterms of a Boolean function.

- In this section, we have discussed 2- 3- and 4-input K-maps. This method can be extended to any number of inputs through the use of multiple tables.

Recapping the rules of K-map simplification:

- Groupings can contain only 1s; no 0s.

- Groups can be formed only at right angles; diagonal groups are not allowed.

- The number of 1s in a group must be a power of 2 even if it contains a single 1.

- The groups must be made as large as possible.

- Groups can overlap and wrap around the sides of the K-map.

- Use don't care conditions when you can.

- Redundancy must be reduced

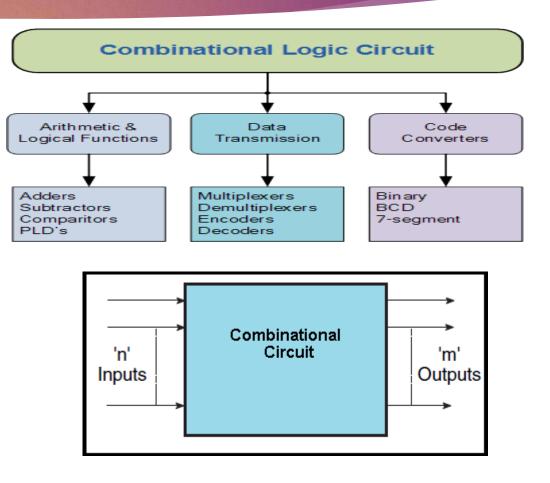

#### Lecture of Module 3

#### **Combinational Circuits**

#### Overview

- Introduction

- ► Half Adder

- **Full Adder**

- ► Half Subtractor

- Full Subtractor

- Ripple/Parallel Adder

- Adder-Subtractor

- Look-ahead carry Adder

#### Introduction

The outputs of **Combinational Logic Circuits** are only determined by the logical function of their current input state(s), logic "0" or(and) logic "1", at any given instant.

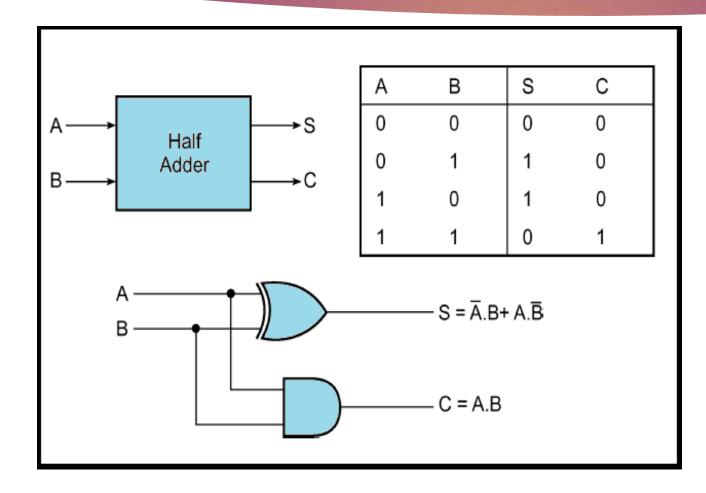

Combinational logic circuits give us many useful devices.

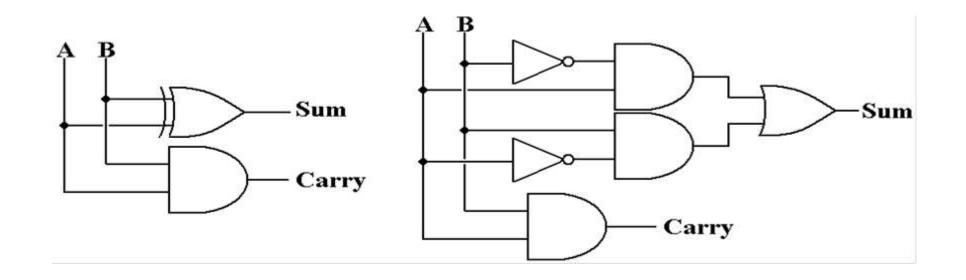

One of the simplest is the *half adder*, which finds the sum of two bits.

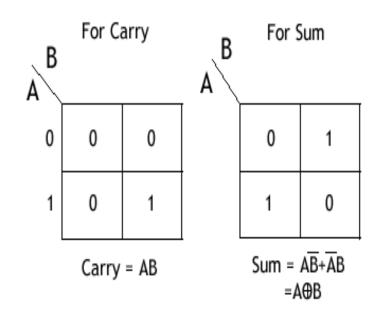

#### Half Adder

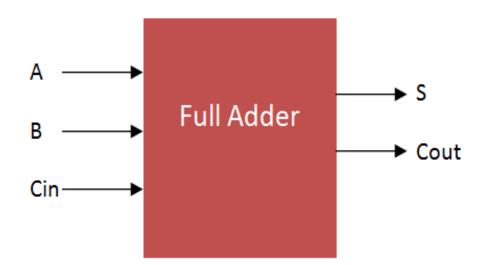

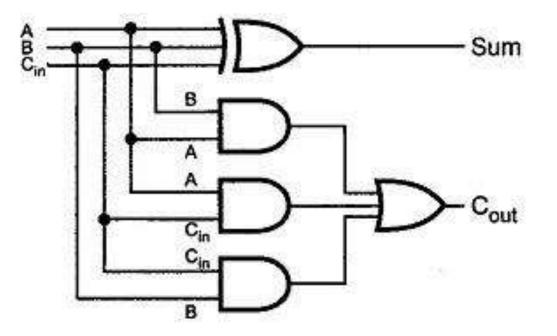

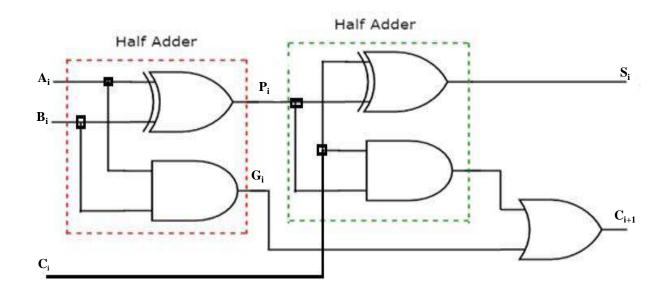

## Full Adder

|   | inputs | Outputs |     |         |

|---|--------|---------|-----|---------|

| A | B      | C – IN  | Sum | C - Out |

| 0 | 0      | 0       | 0   | 0       |

| 0 | 0      | 1       | 1   | 0       |

| 0 | 1      | 0       | 1   | 0       |

| 0 | 1      | 1       | 0   | 1       |

| 1 | 0      | 0       | 1   | 0       |

| 1 | 0      | 1       | 0   | 1       |

| 1 | 1      | 0       | 0   | 1       |

| 1 | 1      | 1       | 1   | 1       |

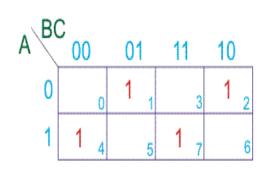

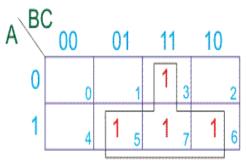

K-map for Sum (S)

K-map for Carry (Cout)

S = ABC+ABC+ABC+ABC

$S=\!A\oplus B\oplus C$

C=AB+BC+CA

#### в $\mathbf{C}$ A $\overline{\mathbf{A}}\overline{\mathbf{B}}\mathbf{C}$ **ĀBC** Sum ABC BC $\mathbf{AC}$ Carry AB

S = ABC+ABC+ABC+ABC

$S{=}A \oplus B \oplus C$

C=AB+BC+CA

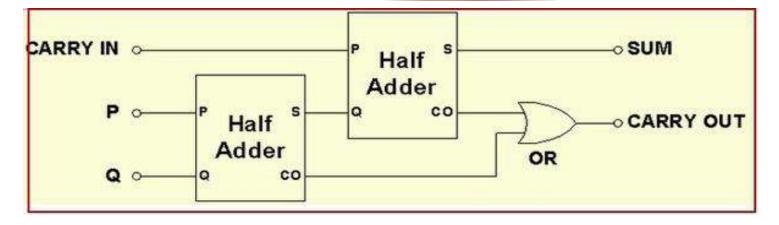

#### Full Adder using Half Adders

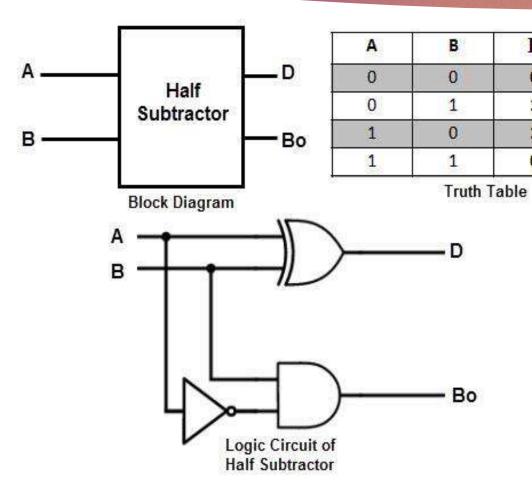

#### Half Subtractor

For D:

Bo

0

1

0

0

D

0

1

1

0

D = A ⊕ B

B

В

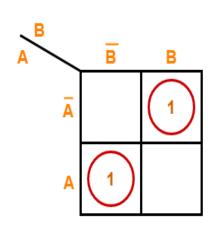

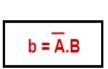

K Maps

For b:

Α

в

Ā

Α

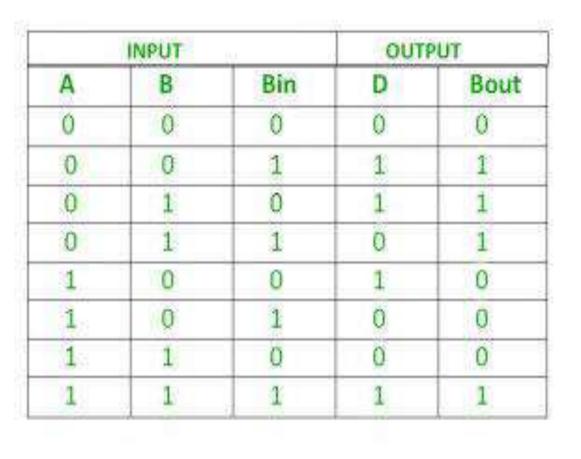

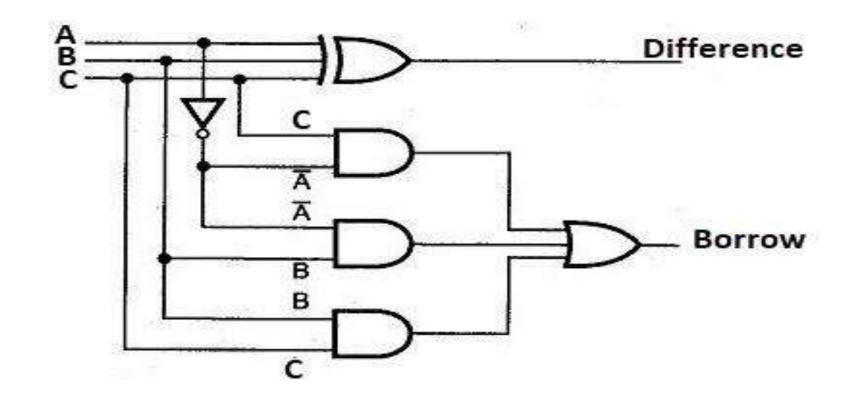

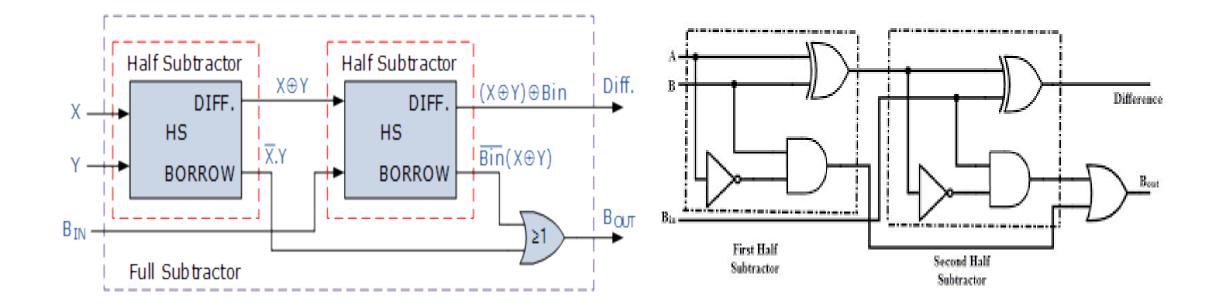

#### Full Subtractor

For D:

| $B_{out} = \overline{A}B + (\overline{A} + B)B_{in}$ |

|------------------------------------------------------|

|------------------------------------------------------|

## Full Subtractor using Half Subtractor

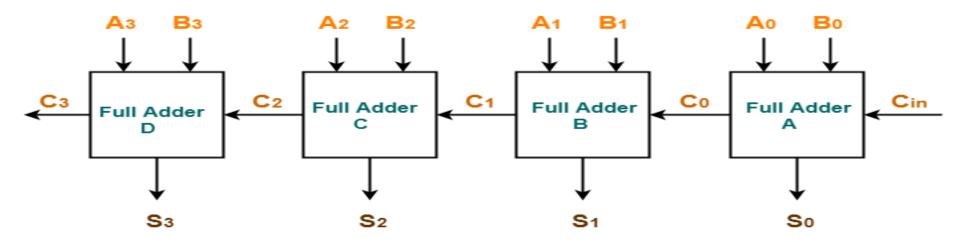

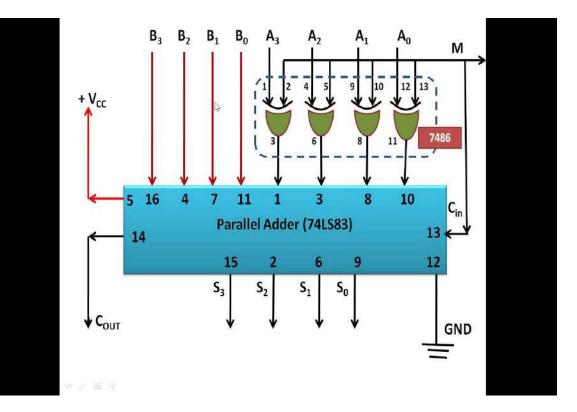

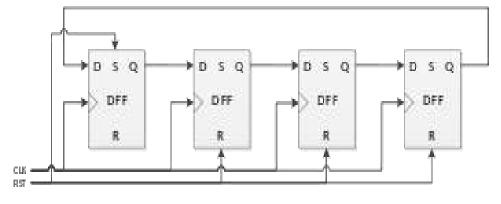

#### Ripple/ Parallel Adder

- Just as we combined half adders to make a full adder, full adders can connected in series.

- The carry bit "ripples" from one adder to the next; hence, this configuration is called a *ripple-carry adder*.

4-bit Ripple Carry Adder

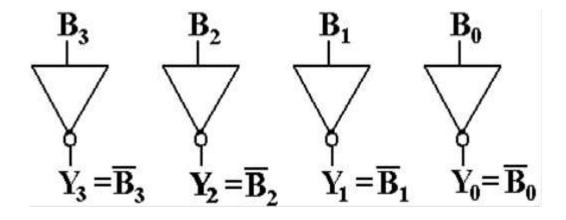

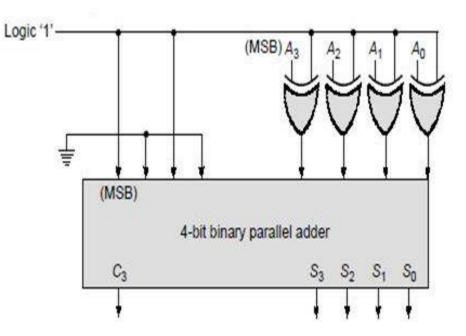

#### **One's Complement Circuit**

In order to make an adder/subtractor, it is necessary to use a gate that can either pass the value through or generate its one's-complement.

The exclusive OR gate, XOR, is exactly what we need.

$B_{3} \qquad B_{2} \qquad B_{1} \qquad B_{0} \qquad Neg$   $V_{3} \qquad V_{2} \qquad V_{1} \qquad V_{0}$ If Neg = 0 Then  $Y_{3} = B_{3}, Y_{2} = B_{2}, Y_{1} = B_{1}, \text{ and } Y_{0} = B_{0}$ If Neg = 1 Then  $Y_{3} = \overline{B}_{3}, Y_{2} = \overline{B}_{2}, Y_{1} = \overline{B}_{1}, \text{ and } Y_{0} = \overline{B}_{0}$ This is controlled by a binary signal: Neg. Let B = 1011.

If Neg = 0, then Y = 1011.

If Neg = 1, then Y = 0100.

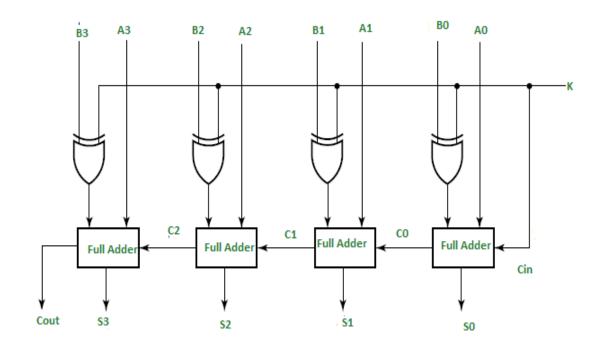

### Adder-Subtractor

- In any combinational circuit, the signal must propagate through the gates before the correct output is available in the output terminal.

- The total propagation time equal to the propagation delay of a typical gate times multiplied with the gate levels in the circuit.

- ► The propagation delay time in a parallel adder is the time it takes the carry to propagate through the full adder.

- In each full adder the carry out from the carry in passes through two gate levels.

- ▶ For n-bit parallel adder the total gate delay will be 2n.

- So, the carry propagation time is a limiting factor on the speed with which two numbers are added in parallel.

- ► To avoid that another adder is widely used which employs the principle of Look-ahead carry.

- The adder designed using the principle of Look-ahead carry is called as Look-ahead carry adder or Carry look-ahead adder.

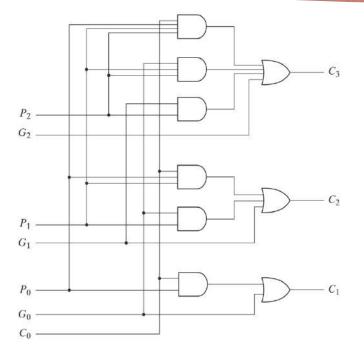

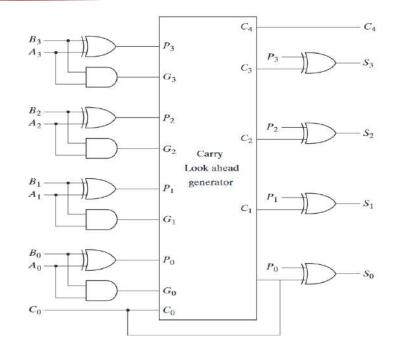

### Look-Ahead Carry Adder

$P_i = A_i \boldsymbol{\Theta} B_i$  $G_i = A_i B_i$

The output Sum and Carry can be expressed as:

$S_i = P_i \bigoplus Ci$  $C_{i+1} = G_i + P_i C_i$

$G_i$  is called as carry generator and  $P_i$  is called as carry propagator.

These equations show that a carry signal will be generated in two cases:

1) if both bits A<sub>i</sub> and B<sub>i</sub> are 1

2) if either A<sub>i</sub> or B<sub>i</sub> is 1 and the carry-in C<sub>i</sub> is 1.

Let's apply these equations for a 4-bit adder:

$$C_{1} = G_{0} + P_{0}C_{0}$$

$$C_{2} = G_{1} + P_{1}C_{1} = G_{1} + P_{1}(G_{0} + P_{0}C_{0}) = G_{1} + P_{1}G_{0} + P_{1}P_{0}C_{0}$$

$$C_{3} = G_{2} + P_{2}C_{2} = G_{2} + P_{2}G_{1} + P_{2}P_{1}G_{0} + P_{2}P_{1}P_{0}C_{0}$$

$$C_{4} = G_{3} + P_{3}C_{3} = G_{3} + P_{3}G_{2} + P_{3}P_{2}G_{1} + P_{3}P_{2}P_{1}G_{0} + P_{3}P_{2}P_{1}P_{0}C_{0}$$

- These expressions show that  $C_2$ ,  $C_3$  and  $C_4$  do not depend on its previous carry-in.

- Therefore  $C_4$  does not need to wait for  $C_3$  to propagate.

- As soon as  $C_0$  is computed,  $C_4$  can reach steady state.

- The same is also true for  $C_2$  and  $C_3$ .

- The general expression is

$C_{i+1} = G_i + P_i G_{i-1} + P_i P_{i-1} G_{i-2} + \dots P_i P_{i-1} \dots P_2 P_1 G_0 + P_i P_{i-1} \dots P_1 P_0 C_0.$

• This is a two level circuit

Carry Look-Ahead Generator

Full Adder with Look-Ahead Carry

Total 4 gate delay: One gate delay for  $P_i$  and  $G_i$  generator, two gate delay for Carry generator and one gate delay for Sum generator.

Advantages:

- •CLA Adders generate the carry-in for each full adder simultaneously, by using simplified equations involving  $P_i$ ,  $G_i$ , and  $C_{in}$ .

- •This system reduces the propagation delay.

- •This is because the output carry at any stage is dependent only on the first Carry signal given at the input.

- •It is the fastest adder when compared to other addition mechanisms.

#### Disadvantages:

•The carry look-ahead adder circuit gets more complicated as the number of variables increase.

•The circuit for a carry look-ahead adder is expensive as it involves more hardware.

•As the number of variables increases, the circuit implements more hardware.

•Thus, when the carry look-ahead adder is implemented as an IC, the area is bound to increase.

#### **Ripple Carry Adder vs. Carry Look Ahead Adder**

| Ripple Carry Adder                                                                                                      | Carry Look Ahead Adder                                                                                                  |

|-------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|

| The Carry bit passes through a long logic chain through the entire circuit.                                             | The Carry bit enters in the system only at the input.                                                                   |

| As the full adder blocks are dependent on their predecessor blocks' carry value, the entire system works a little slow. | Since the entire system depends on the first carry input, the computations are very quick, making it the fastest adder. |

| It has a simple repetitive design.                                                                                      | Has a slightly complicated design with many logic gates                                                                 |